# SHA-SHIB GROUP OF INSTITUTIONS Training Notes

## Module 05- Digital Techniques Electronic Instrument Systems

#### UNCONTROLLED COPY

- The information in this book is for study/ training purposes only and no revision service will be provided to the holder.

- While carrying out a procedure/ work on aircraft/ aircraft equipment you must always refer to the relevant Aircraft Maintenance Manual or Equipment Manufacturer's Handbook.

- For health and safety in the workplace you should follow the regulations/ Guidelines as specified by the Equipment Manufacturer, your company, National Safety Authorities and National Governments.

#### Copyright Notice

© Copyright. All worldwide rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form by any other means whatsoever: i.e. photocopy, electronic, mechanical recording or otherwise without the prior written permission of Sha-Shib Group of Institutions.

### Knowledge Levels - Category A, B1, B2, B3 and C Aircraft Maintenance Licence

Basic knowledge for categories A, B1, B2 and B3 are indicated by the allocation of knowledge levels indicators (1, 2 or 3) against each application subject. Category C applicants must meet either the category B1 or the category B2 basic knowledge levels.

The knowledge level indicators are defined as follows:

#### LEVEL 1

- A familiarization with the principal elements of the subject.

- Objectives: The applicant should be familiar with the basic elements of the subject.

- The applicant should be able to give a simple description of the whole subject, using common words and examples.

- The applicant should be able to use typical terms.

#### LEVEL 2

- A general knowledge of the theoretical and practical aspects of the subject.

- · An ability to apply that knowledge.

- Objectives: The applicant should be able to understand the theoretical fundamentals of the subject.

- The applicant should be able to give a general description of the subject using, as appropriate, typical examples.

- The applicant should be able to use mathematical formulae in conjunction with physical laws describing the subject.

- The applicant should be able to read and understand sketches, drawings and schematics describing the subject.

- The applicant should be able to apply his knowledge in a practical manner using detailed procedures.

#### LEVEL 3

- A detailed knowledge of the theoretical and practical aspects of the subject.

- A capacity to combine and apply the separate elements of knowledge in a logical and comprehensive manner.

- Objectives: The applicant should know the theory of the subject and interrelationships with other subjects.

- The applicant should be able to give a detailed description of the subject using theoretical fundamentals and specific examples.

- The applicant should understand and be able to use mathematical formulae related to the subject.

- The applicant should be able to read, understand and prepare sketches, simple drawings and schematics describing the subject.

- The applicant should be able to apply his knowledge in a practical manner using manufacturer's instructions.

- The applicant should be able to interpret results from various sources and measurements and apply corrective action where appropriate.

## -: DGCA MODULARISATION :-

#### CAR - 66 ISSUE II R 2

### (LICENSING OF AIRCRAFT MAINTENANCE ENGINEERS)

## DIRECTORATE GENERAL OF CIVIL AVIATION

TECHNICAL CENTRE, OPP SAFDURJUNG AIRPORT, NEW DELHI

| Modules | Subject                                                     | A or B1 Aero             | plane with              | A or B1 Heli             | copter with             | B2       |  |

|---------|-------------------------------------------------------------|--------------------------|-------------------------|--------------------------|-------------------------|----------|--|

|         |                                                             | Turbine<br>Engine<br>(s) | Piston<br>Engine<br>(s) | Turbine<br>Engine<br>(s) | Piston<br>Engine<br>(s) | Avionics |  |

| 1       | -                                                           |                          | Not Applical            | ole                      |                         | 30       |  |

| 2       |                                                             |                          | Not Applicab            | le                       |                         |          |  |

| 3       | ELECTRICAL FUNDAMENTALS                                     | X                        | X                       | X                        | X                       | X        |  |

| 4       | ELECTRONIC FUNDAMENTALS                                     | Х                        | X                       | X                        | X                       | X        |  |

| 5       | DIGITAL TECHNIQUES<br>ELECTRONIC INSTRUMENT<br>SYSTEMS      | X                        | X                       | X                        | X                       | X        |  |

| 6       | MATERIALS AND HARDWARE                                      | X                        | X                       | X                        | X                       | X        |  |

| 7A      | MAINTENANCE PRACTICES                                       | X                        | X                       | X                        | X                       | X        |  |

| 7B      | MAINTENANCE PRACTICES                                       |                          |                         |                          |                         |          |  |

| 8       | BASIC AERODYNAMICS                                          | Х                        | X                       | Х                        | Х                       | X        |  |

| 9A      | HUMAN FACTORS                                               | Х                        | Х                       | X                        | X                       | X        |  |

| 9B      | HUMAN FACTORS                                               |                          |                         |                          |                         |          |  |

| 10      | AVIATION LEGISLATION                                        | Х                        | X                       | Х                        | Х                       | X        |  |

| 11A     | TURBINE AEROPLANE AERODYNAMICS, STRUCTURES AND SYSTEMS      | х                        |                         |                          |                         |          |  |

| 11B     | PISTON AEROPLANE AERODYNAMICS, STRUCTURES AND SYSTEMS       |                          | X                       |                          |                         |          |  |

| 11C     | PISTON AEROPLANE<br>AERODYNAMICS, STRUCTURES<br>AND SYSTEMS |                          |                         |                          |                         |          |  |

| 12      | HELICOPTER AERODYNAMICS,<br>STRUCTURES AND SYSTEMS          |                          |                         | X                        | X                       |          |  |

| 13      | AIRCRAFT AERODYNAMICS,<br>STRUCTURES AND SYSTEMS            |                          |                         |                          |                         | X        |  |

| 14      | PROPULSION                                                  |                          |                         |                          |                         | х        |  |

| 15      | GAS TURBINE ENGINE                                          | X                        |                         | X                        |                         |          |  |

| 16      | PISTON ENGINE                                               |                          | Х                       |                          | Х                       |          |  |

| 17A     | PROPELLER                                                   | X                        | X                       |                          |                         |          |  |

| 17B     | PROPELLER                                                   |                          |                         |                          |                         |          |  |

## TRAINING NOTES MODULE: 05

SUBJECT NAME: DIGITAL TECHNIQUES ELECTRONIC INSTRUMENT SYSTEMS

| UNIT      | OBJECTIVE                                                                                         |        |               |  |

|-----------|---------------------------------------------------------------------------------------------------|--------|---------------|--|

| NO.       |                                                                                                   | B1     | B2            |  |

| - 4       | 5.1 Electronic Instrument Systems                                                                 |        |               |  |

| 5.1       | Typical systems arrangements and cockpit layout of electronic                                     | 2      | 2             |  |

|           | instrument systems.                                                                               |        |               |  |

|           | 5.2 Numbering Systems Numbering systems: binary, octal and hexadecimal;                           |        |               |  |

| 5.2       | Demonstration of conversions between the decimal and binary, octal                                | 2      | 2             |  |

|           | and hexadecimal systems and vice versa.                                                           |        |               |  |

|           | 5.3 Data Conversion                                                                               |        |               |  |

| F 2       | Analogue Data, Digital Data;                                                                      | 1      | 1             |  |

| 5.3       | Operation and application of analogue to digital, and digital to                                  | 1      | 1             |  |

|           | analogue converters, inputs and outputs, limitations of various types.                            |        |               |  |

|           | 5.4 Data Buses                                                                                    | D24.59 | 25414.3       |  |

| 5.4       | Operation of data buses in aircraft systems, including knowledge of                               | 2      | 2             |  |

|           | ARINC and other specifications.                                                                   |        |               |  |

|           | 5.5 Logic Circuits                                                                                |        |               |  |

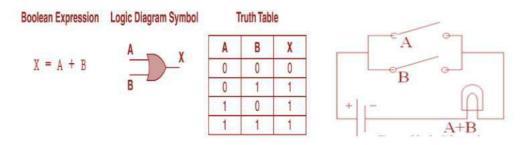

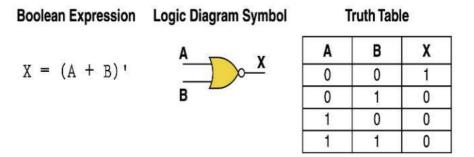

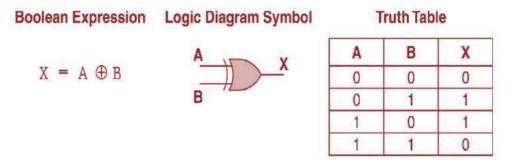

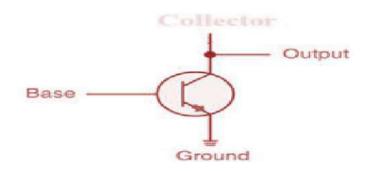

|           | (a) Identification of common logic gate symbols, tables and equivalent                            | 1      | 1             |  |

| 5.5       | circuits;                                                                                         | 1      | 1             |  |

|           | Applications used for aircraft systems, schematic diagrams.  (b)Interpretation of logic diagrams. |        |               |  |

|           | 5.6 Basic Computer Structure                                                                      |        |               |  |

|           | (a)                                                                                               |        |               |  |

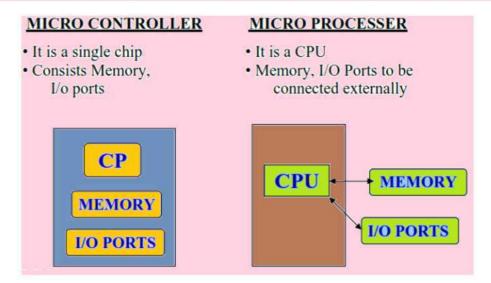

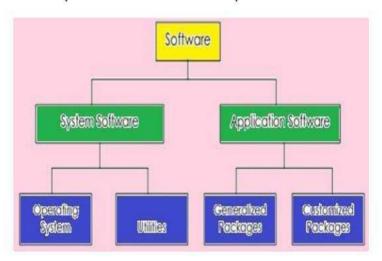

|           | Computer terminology (including bit, byte, software, hardware, CPU,                               |        |               |  |

|           | IC, and various memory devices such as RAM, ROM, PROM);                                           |        |               |  |

|           | Computer technology (as applied in aircraft systems).                                             |        |               |  |

|           | (b)                                                                                               |        |               |  |

| 5.6       | Computer related terminology;                                                                     | 1      | 1             |  |

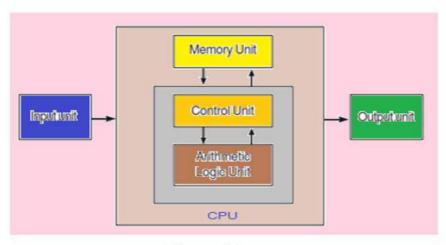

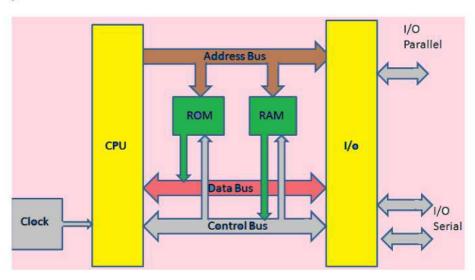

| 5.0       | Operation, layout and interface of the major components in a micro                                | _      | <del></del> . |  |

|           | computer including their associated bus systems;                                                  |        |               |  |

|           | Information contained in single and multi address instruction words; Memory                       |        |               |  |

|           | associated terms;                                                                                 |        |               |  |

|           | Operation of typical memory devices;                                                              |        |               |  |

|           | Operation, advantages and disadvantages of the various data storage systems.                      |        |               |  |

|           | 5.7 Microprocessors                                                                               |        |               |  |

|           | Functions performed and overall operation of a microprocessor;                                    |        |               |  |

| 5.7       | Basic operation of each of the following microprocessor elements:                                 | 2      | 2             |  |

|           | control and processing unit, clock, register, arithmetic logic unit.                              |        |               |  |

| ,         | 5.8 Integrated Circuits                                                                           |        |               |  |

| E 0       | Operation and use of encoders and decoders                                                        | 2      | 2             |  |

| 5.8       | Function of encoder types                                                                         |        | 2             |  |

|           | Uses of medium, large and very large scale integration.                                           |        |               |  |

| 192200027 | 5.9 Multiplexing                                                                                  | 2000   | 5000          |  |

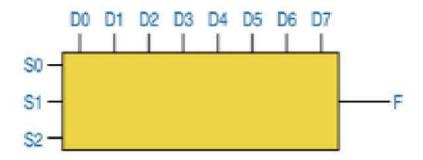

| 5.9       | Operation, application and identification in logic diagrams of                                    | 2      | 2             |  |

|           | multiplexers and demultiplexers.                                                                  |        |               |  |

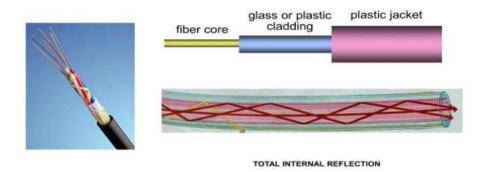

| 5.10 | 5.10 Fibre Optics  Advantages and disadvantages of fibre optic data transmission over electrical wire propagation; Fibre optic data bus; Fibre optic related terms; Terminations; Couplers, control terminals, remote terminals; Application of fibre optics in aircraft systems.                                                                                                                                                                                                                                                                                                                                                                        |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

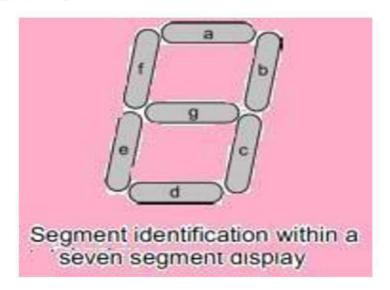

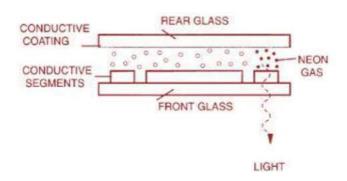

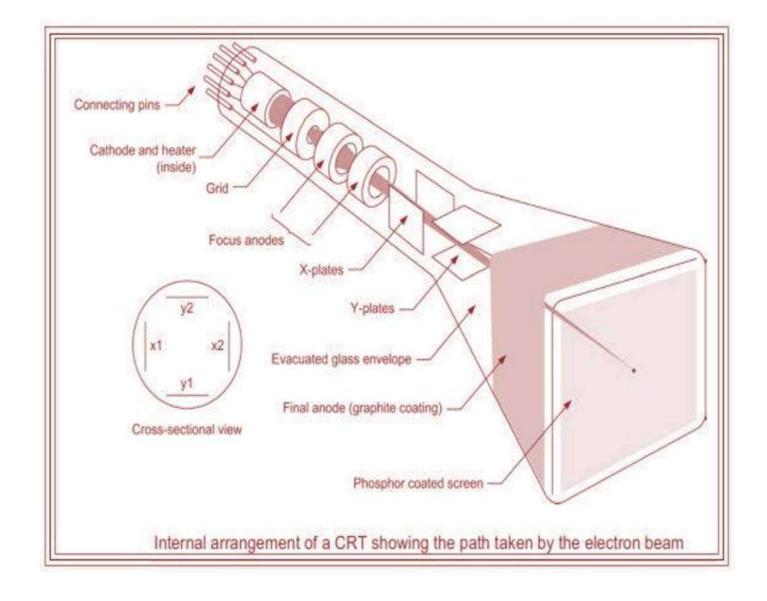

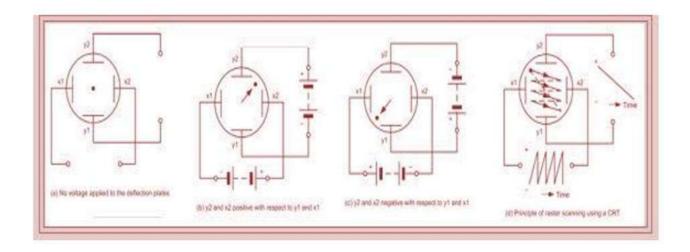

| 5.11 | 5.11 Electronic Displays Principles of operation of common types of displays used in modern aircraft, including Cathode Ray Tubes, Light Emitting Diodes and Liquid Crystal Display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 5.12 | 5.11 Electronic Displays Principles of operation of common types of displays used in modern aircraft, including Cathode Ray Tubes, Light Emitting Diodes and Liquid Crystal Display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 5.13 | 5.13 Software Management Control  Awareness of restrictions, airworthiness requirements and possible catastrophic effects of unapproved changes to software programmes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

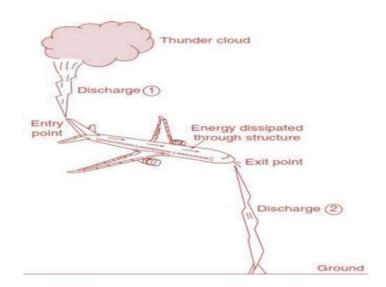

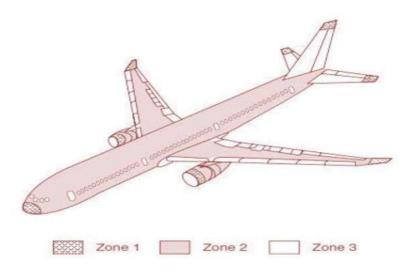

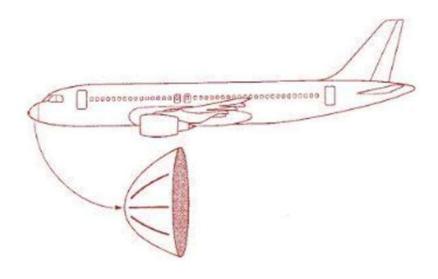

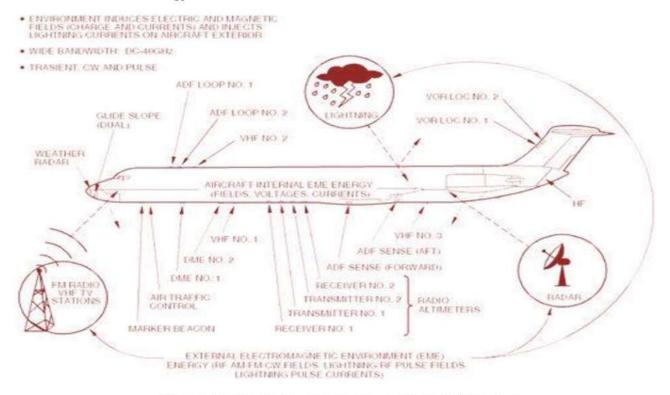

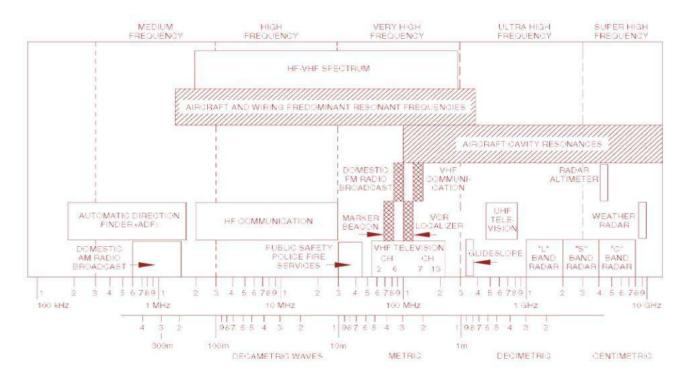

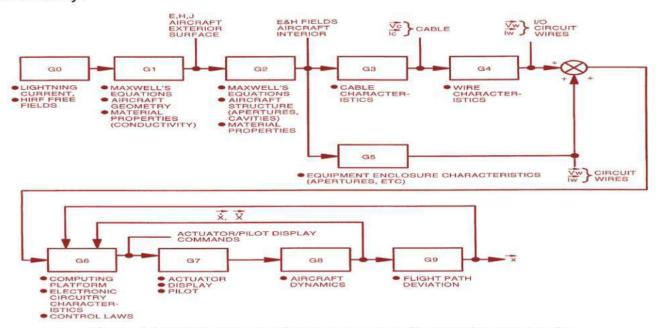

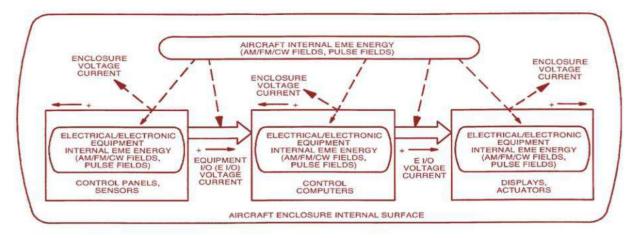

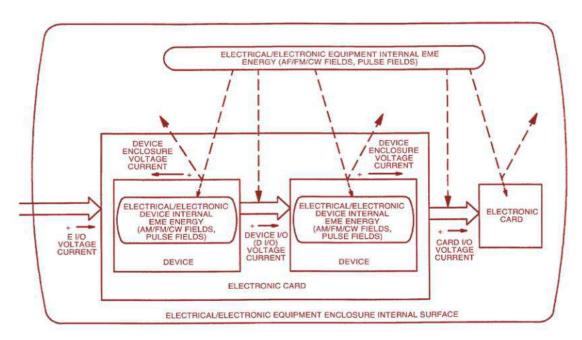

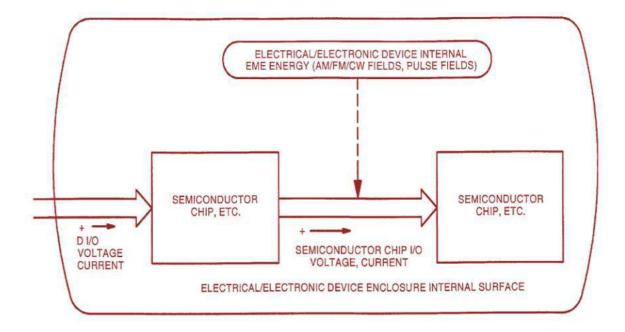

| 5.14 | 5.14 Electromagnetic Environment Influence of the following phenomena on maintenance practices for electronic system: EMC-Electromagnetic Compatibility EMI-Electromagnetic Interference HIRF-High Intensity Radiated Field Lightning/lightning protection                                                                                                                                                                                                                                                                                                                                                                                               |  |

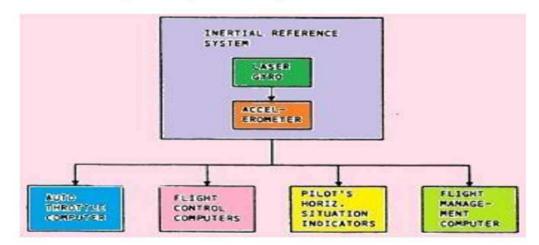

| 5.15 | 5.15 Typical Electronic/Digital Aircraft Systems General arrangement of typical electronic/digital aircraft systems and associated BITE(Built In Test Equipment) testing such as: (a) For B1 and B2 only: ACARS-ARINC Communication and Addressing and Reporting System EICAS-Engine Indication and Crew Alerting System FBW-Fly by Wire FMS-Flight Management System IRS-Inertial reference system (b) For B1, B2 and B3: ECAM-Electronic Centralised Aircraft Monitoring EFIS-Electronic Flight Instrument System GPS-Global Positioning System TCAS-Traffic Collission Avoidance system Integrated modular Avionica Cabin System , Information system |  |

Module 05: Enabling Objectives and Certification Statement

## **Certification Statement**

These Study Notes comply with the syllabus of DGCA, CAR – 66 (Appendix I) and the associated Knowledge Levels as specified.

## **REVISION LOG**

| Sr. No. | Issue / Revision<br>No. | Issue / Revision<br>Date | Pages Revised | Signature |

|---------|-------------------------|--------------------------|---------------|-----------|

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

| =       |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

|         |                         |                          |               |           |

## **TABLE OF CONTENTS**

| <u>CHAPTER</u> <u>PAGE</u>                            |

|-------------------------------------------------------|

| UNIT 1 – Electronics Instrument Systems               |

| UNIT 2 – Numbering Systems                            |

| UNIT 3 – Data Conversion                              |

| UNIT 4 – Data Bus36-43                                |

| UNIT 5 – Logic Circuits44-55                          |

| UNIT 6 – Basic Computer Structure56-69                |

| UNIT 7 – Microprocessors70-80                         |

| UNIT 8 – Integrated Circuits                          |

| UNIT 9 – Multiplexing85-96                            |

| UNIT 10 – Fiber Optics97-113                          |

| UNIT 11 – Electronic Displays                         |

| UNIT 12 – Electrostatic Sensitive Devices             |

| UNIT 13 – Software Management Control                 |

| UNIT 14 – Electromagnetic Environment                 |

| UNIT 15 – Typical Electronic/Digital Aircraft Systems |

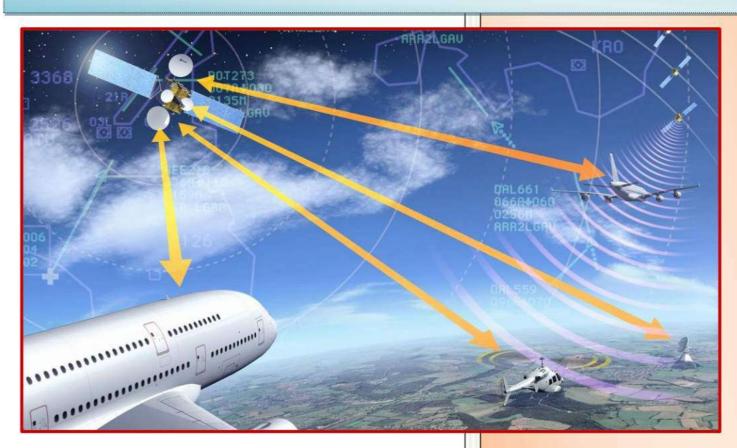

### 5.1 ELECTRONICS INSTRUMENT SYSTEMS

Typical systems arrangements and cockpit layout of electronic instrument systems.

#### FLIGHT INSTRUMENTS

Flight instruments of paramount importance in any aircraft is the system (or systems) used for sensing and indicating the aircraft's attitude, heading, altitude and speed. In early aircraft, these instruments were simple electro- mechanical devices. Indeed, when flying under visual flight rules (VFR) rather than instrument flight rules (IFR) the pilot's most important source of information about what the aircraft was doing would have been the view out of the cockpit window! Nowadays, sophisticated avionic and display technology, augmented by digital logic and computer systems, has made it possible for an aircraft to be flown (with a few possible exceptions). Various instruments are used to provide the pilot with flight-related information, such as the aircraft's current heading, airspeed and attitude.

Modern aircraft use electronic transducers and electronic displays and indicators. Cathode ray tubes (CRT) and liquid crystal displays (LCD) are increasingly used to display this information in what has become known as a 'glass cockpit'. Modern passenger aircraft generally have a number of such displays, including those used for primary flight data and multi- function displays that can be configured to display a variety of information. We shall begin this section with a brief review of the basic flight instruments.

Basic flight instruments Crucial among the flight instruments fitted to any aircraft are those that indicate the position and attitude of the aircraft. These basic flight instruments are required to display information concerning:

- heading

- altitude

- airspeed

- rate of turn

- rate of climb (or descent)

- attitude (relative to the horizon).

The typical instrument displays shown in Figures 1.2–1.8.

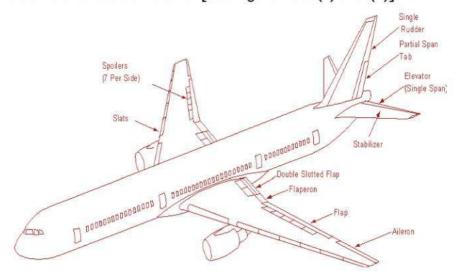

Fig. 1.1 Boeing 757 Flight Instrument &

## **Displays**

1.2 Altimeter

1.4 Attitude indicator

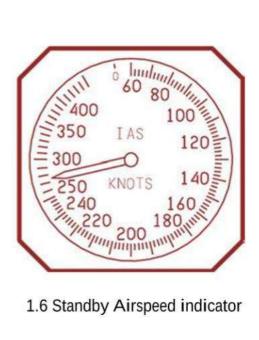

1.6 Standby Airspeed indicator

1.3 Standby Altimeter

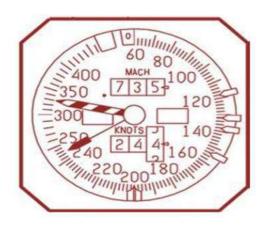

1.5 Airspeed indicator

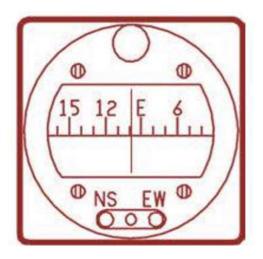

1.7 Standby magnetic compass

1.8 Standby vertical speed indicator

1.9 Typical Airspeed indicator

#### COCKPIT LAYOUTS

Major developments in display technology and the introduction of sophisticated increasingly aircraft computer systems have meant that cockpit layouts have been subject to continuous change over the past few decades. At the same time, aircraft designers have had to respond to the need to ensure that the flight crew are not over burdened with information and that relevant data is presented in an appropriate form and at the time it is needed.

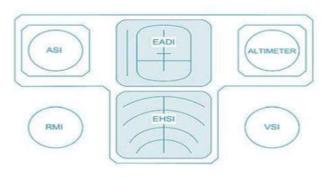

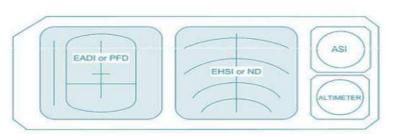

Figure 1.10 shows how the modern **EFIS** layouts have evolved progressively from the basic instrument configuration found in non-EFIS aircraft. Maintaining the relative position of the instruments has been important in allowing pilots to adapt from one aircraft type to another. At the same time, the large size of modern CRT and LCD displays, coupled with the ability of these instruments to display combined data (for example, heading, airspeed and altitude) has led to a less-cluttered instrument panel (see Figures

(a) Basic 'T' flight instrument configuration

(b) Basic EFIS flight instrument configuration

(c) Enhanced EFIS flight instrument configuration

1.241.26). Lastly, a number of stand by

1.10 Evolution of EFIS System

(or secondary) instruments are made available in order to provide the flight crew with reference information which may become invaluable in the case of a malfunction in the computer system.

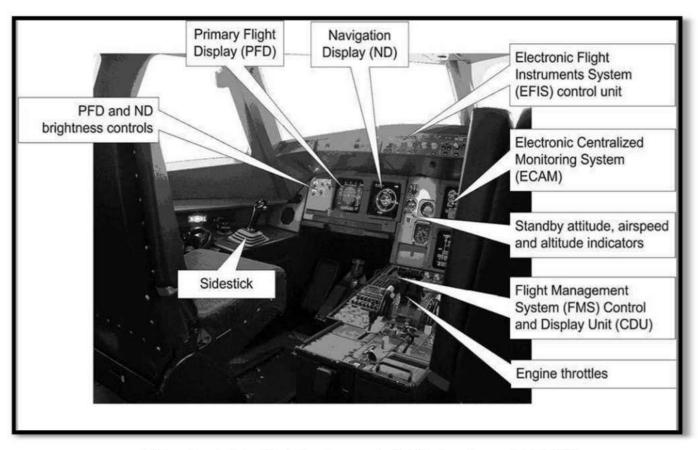

1.11 Captain's Flight Instruments & Display Layout on A320

1.12 Upgraded Flight Instrument on an Aero Commander690A

## **ELECTRONICS FLIGHT INSTRUMENT SYSTEM (EFIS)**

Most of the Passenger aircraft use Electronic Flight Instrument System (EFIS) displays that has become known as the 'glass Cockpit. EFIS provides large, clear, high-resolution displays which are easy to view under wide variations of ambient light intensity. Displays can be independently selected and configured as required by the captain and first officer and the ability to display information from various data sources in a single display makes it possible for the crew to rapidly assimilate the information that they need. A notable disadvantage of EFIS is a significant increase in EMI. The two most commonly featured EFIS instruments are the Electronic Horizontal Situation Indicator (EHSI) and the Electronic Attitude Direction Indicator (EADI).

The EFIS uses input data from several sources including

- VOR/ILS/MLS

- TACAN (see later)

- Pitch, roll, heading rate and acceleration data from anAttitude Heading System Reference (AHRS) or conventional vertical gyro

- Compass system

- Radar altimeter

- Air data system

- Distance Measuring Equipment (DME)

- Area Navigation System (RNAV)

- Vertical Navigation System (VNAV)

- Weather Radar System (WXR)

- Automatic Finder (ADF)

Typical EFIS displays are shown in fig 1.13 & 1.14.

1.13 Typical EFIS Display forBoeing

1.14 Typical EFIS for Airbus

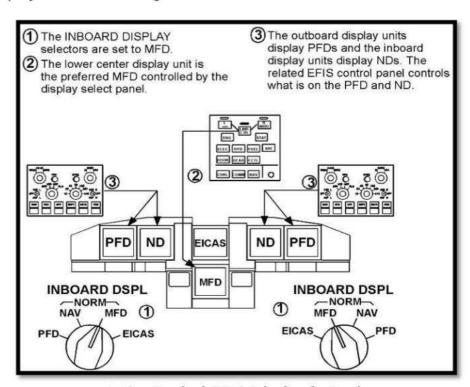

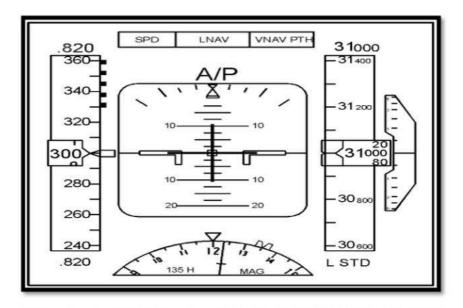

### PRIMARY FLIGHT DISPLAY (PFD)

The PFDs present a dynamic color display of all the parameters necessary for flight path control. The PFDs provide the following Information:

- Flight Mode Annunciation

- Airspeed

- Altitude

- Vertical Speed

- Attitude

- Steering Information

- Radio Altitude

- Instrument Landing System Display

- Approach Minimums

- Heading/ Track Indications

- Time Critical Warnings

Failure flags are displayed for airplane system failures. Displayed information is removed or replaced by dashes if no valid information is available to the display system (because of out-of range or malfunctioning navigation aids). Displays are removed when a source fails or when no system source information is available.

Expanded mode with a partial compass rose and a centered mode with a full compass rose.

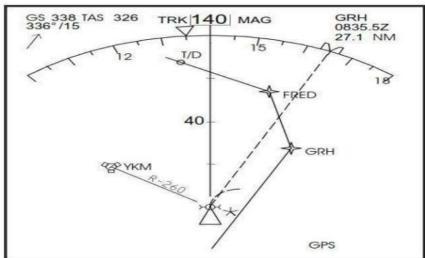

#### ND Modes / MAP Mode

The MAP mode is recommended for most phases of flight. Presented track up, this mode shows airplane position relative to the route of flight against a moving map background.

1.15 Typical PFD display NAVIGATION DISPLAY (ND)

The NDs provide a mode-selectable color flight progress display. The modes are: The MAP, VOR, and APP modes can be switched between an

#### VOR AND APPROACH MODES

The VOR and APP modes are presented heading up. The VOR and APP modes display track, heading, and wind speed and direction with VOR navigation or ILS approach information.

#### PLAN MODE

The PLN mode is presented true north up. The active route may be viewed using the STEP prompt on the CDU LEGS pages.

#### ND INFORMATION

#### **HEADING**

Heading is supplied by the FMC or Air Data Inertial Reference System (ADIRS). The ND compass rose can be referenced to magnetic north or true north. The heading reference switch is used to manually select magnetic or true reference. The compass display is automatically referenced to true north when the airplane is north of 82° north or south of 82° south latitude, or near the magnetic poles with the heading reference switch in NORM.

#### TRACK

Track is supplied by the FMC during normal operation and by the CDU when in alternate navigation.

#### TRAFFIC

Traffic information from the TCAS can be displayed on the ND

#### WEATHER RADAR

Weather radar information can be displayed on the ND.

#### FAILURE FLAGS AND MESSAGES

Failure flags are displayed for system failures or invalid information. Indications are removed or replaced by dashes when source system information is not available. The message EXCESS DATA is displayed if the amount of information sent to the ND exceeds the display capability. When this occurs, the primary display system removes information from the center of the display outward; information near the outer selected range area is still displayed. The message can be removed by:

- Reducing the amount of map information,

- Reducing range, or

- Deselecting one or more of the EFIS control panel map switches (STA, WPT, ARPT, DATA, POS).

#### 1.16 Typical ND display when POS (Position) Map Switchis Selected

## ECAM (ENHANCED SYSTEM)

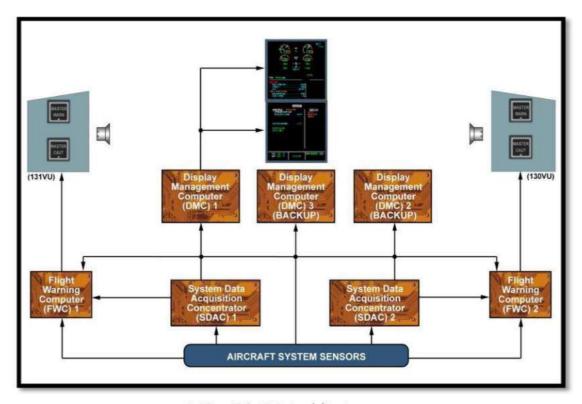

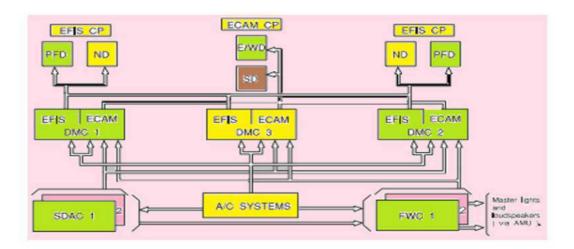

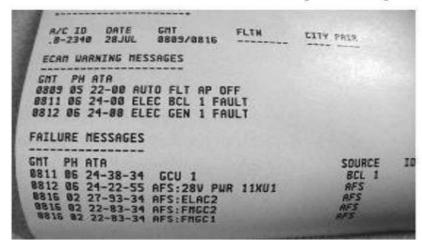

On the enhanced system, the only difference on this schematic is that DMC 1 supplies both ECAM displays and DMC 2 is also a backup for ECAM displays. The DMCs acquire data and transmit it to the Display Units which generate the images. Under normal circumstances, DMC 1 supplies both ECAM display & DMC 2 and 3 are available as a backup. The FWCs, heart of the ECAM system, receive data from the A/C systems to generate red warnings, the SDACs to generate amber cautions. The FWCs then supply.

- The DMCs for the display of alert messages,

- The attention getters,

- The loudspeakers with aural alerts and synthetic voice messages.

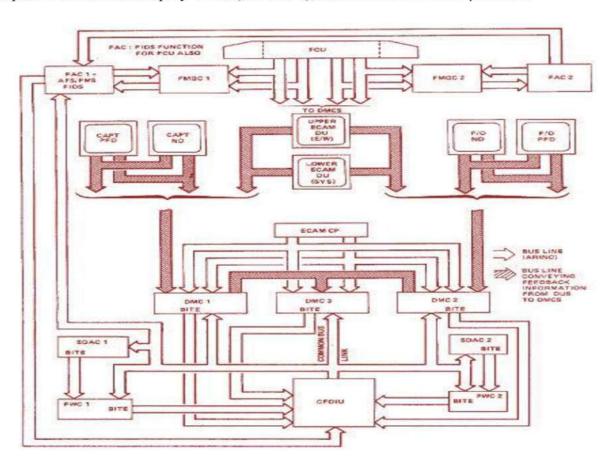

#### ECAM OPERATION GENERAL ARCHITECTURE

The Electronic Centralized Aircraft Monitoring (ECAM) fulfils three main Functions:

- Data acquisition and concentration,

- Data warning computation,

- Warning announcement and data display.

Data acquisition is shared between, The System Data Acquisition Concentrators (SDACs), the Flight Warning Computers (FWCs) and the Display Management Computers (DMCs). Data warning computation and memo information are achieved by the FWCs. Warning announcement and data display is made through loudspeakers and Display Units (DUs). The FWCs give aural and visual

information in order to Know, in real time, all the system failures and dangerous configurations with their level of seriousness, identify the systems or circuits affected by a failure, take the appropriate corrective action

1.17 ECAM Architecture

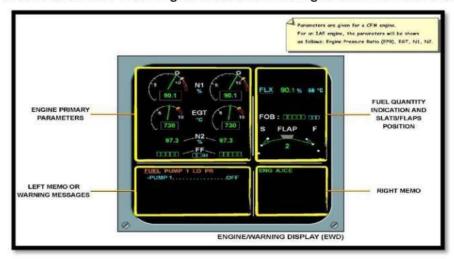

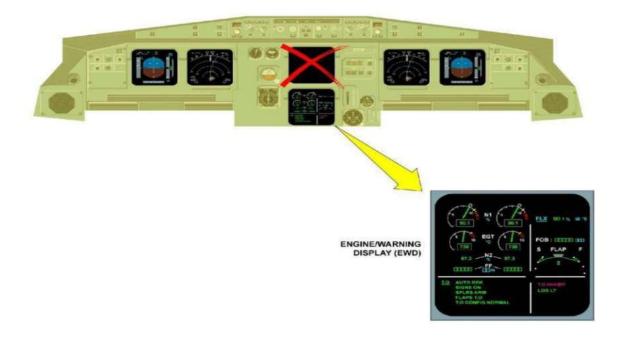

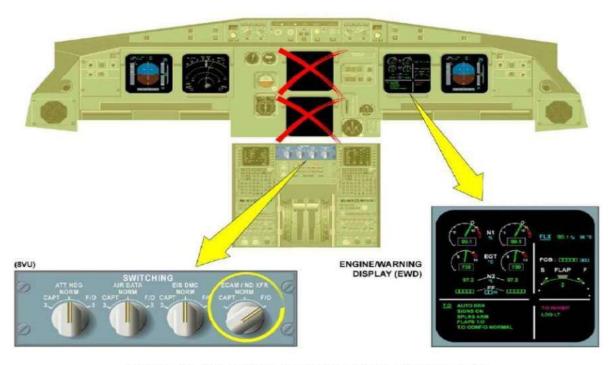

#### ENGINE/WARNING DISPLAY PRESENTATION GENERAL OVERVIEW

The Engine/Warning Display (EWD) is normally on the upper Electronic Centralized Aircraft Monitoring (ECAM) Display Unit (DU). It is divided into two areas: the upper area and the lower area. (See figure 1.18)

- The upper area displays: Engine primary parameters, Fuel On Board (FOB), Slats and flaps position.

- The lower area is used for: Warning and caution messages and Memo messages.

1.18 General Overview of ECAM

#### ENGINE/WARNING DISPLAY AREAS

#### 1. UPPER AREA

The symbols of the upper area are permanently displayed. The parameters are provided in the form of analog and/or digital indications (refer to related chapter for detailed description).

#### 2. LEFT MEMO AREA

Takeoff (TO) or landing memo, normal memo, independent failure messages, or primary failure messages and actions to do are displayed in the left memo area. As soon as a failure is detected, the memo messages are replaced by warning/caution messages.

#### 3. RIGHT MEMO AREA

Normal memo and secondary failure messages are displayed in the right memo area. For example when an engine anti ice P/B is set to ON, ENG Anti ICE appears on the right memo area. During TO and landing, most of the warnings are inhibited to avoid distraction of the crew. For example, at TO, when the second engine is set to TO power and until the aircraft has reachedFigure 1.500 ft, TO INHIB is displayed.

#### TYPE OF FAILURES IN ECAM GENERAL

The failures may be of three different types, independently of their classification. There are 3 separate types of warnings or cautions:

- Those associated with an independent failure,

- Those associated with a primary failure,

- Those associated with a secondary failure.

#### INDEPENDENT FAILURE

An independent failure is a failure, which affects an isolated item of equipment or system without affecting another one. Example: Flight Warning Computer (FWC) 1 failure.

NOTE: An independent failure is displayed with the title underlined.

#### 2. PRIMARY FAILURE

A primary failure is a failure of an item of equipment or system causing the loss of other equipment. Example: Green hydraulic system failure may lead to the loss of a pair of spoilers.

#### SECONDARY FAILURE

A secondary failure is a loss of an item of equipment or system resulting from a primary failure. Example: Loss of a pair of spoilers after a hydraulic system failure. The titles of the system pages corresponding to the secondary failures are indicated on the lower right part of the Engine/Warning Display (EWD) by an asterisk.

NOTE: This part can be used if necessary to display heading titles of warnings if the left part of the EWD is full.

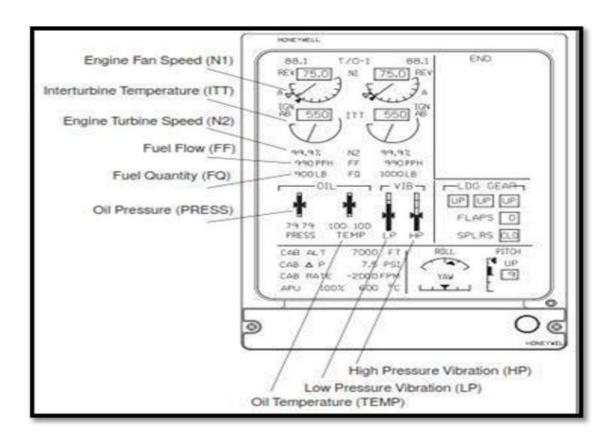

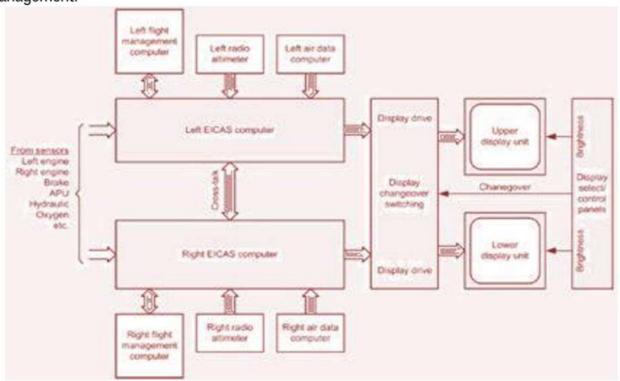

## **ENGINE INDICATION AND CREW ALERTING SYSTEM (EICAS)**

The Engine Indication and Crew Alerting System (EICAS) receive and processes signals from engine and system sensors. The architecture of the system (EICAS) starts from the engine and system sensors. In this system there are two Data Acquisition Units (DAU's) which collect data from systems of all parts of the aircraft. The DAU 1 collects the data from the sources located in the front part of the aircraft and engine # Figure 1. The DAU 2 collects the data from the sources located in the rear part of the aircraft and engine # 2. Either message or indication goes through DAU, where the analog signal is changed to a digital one, and sent to the integrated computer (IC-600). This system also uses reversion switches for display units, data acquisition unit, and symbol generators. The Data Acquisition Unit (DAU) receives analog and digital signals for using them in the EICAS. The following aircraft systems are interfacing with the EICAS for indication and alert functions:

- Power plant

- Landing gear

- Flaps

- Spoilers

- Pressurization

- APU

- Trims

- Brakes

- Hydraulics

- Electrical

- Fuel

- Ice/rain protection

- Air conditioning

- (Aircraft with CAT-III a configuration) Head-up guidance system.

- Oxygen

- Doors

The following aircraft systems are interfacing the EICAS for alerting purposes only:

- Air turbine starter

- Master announcement

- Aural warning

- Central Maintenance Computer (CMC)

- (E) GPWS/Wind shear

- Rudder

- Smoke

- Stall protection system

- Thrust reverser

The integrated architecture of the system uses the EICAS display and MFD's for indications. The Radio Management Units, two separate displays which are normally used for Radio Management purpose, can be used to display EICAS information (engineparameters and critical messages) as a backup in case of failure of an Integrated Computer.

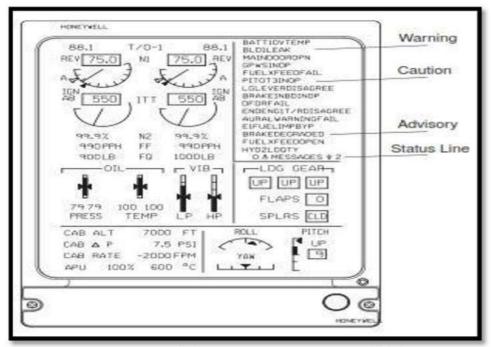

#### **EICAS PRIMARY FORMAT**

The EICAS primary format is always shown at the DU-3, and is divided in three parts:

- Engine Indications

- System Indications

- Crew Alerting

#### ENGINE INDICATION OF OTHER AIRCRAFT SYSTEMS

The most important parameters of the engines are presented on the EICAS primary format on DU 3 Figure 1.19 highlights the Indication of the other aircraft systems those are continuously shown on the EICAS primary Format. The EICAS continuously monitors the status of various aircraft and avionics system, and generates messages for the flight crew members. Each IC-600 receives warning, caution, advisory, and status signals from systems. The IC that controls the EICAS display, which is selected through the reversionary panel, will have the messages displayed. The CAS area location is at the upper right field of the EICAS display. This field has the capability of 16 lines of 18 characters per line. The last line shows the status line. More than 150 messages will be shown on the CAS according to the message type. The message types are warning, caution, and advisory. Warning (red color) messages are displayed on top, followed by caution (amber color) messages, and advisory (cyan color) messages. The newest message will be displayed on top of its respective queue. When a new message occurs, the message will flash.

1.19 Engine indication on EICAS display

1.20 Crew Alerting Messages on EICAS display.

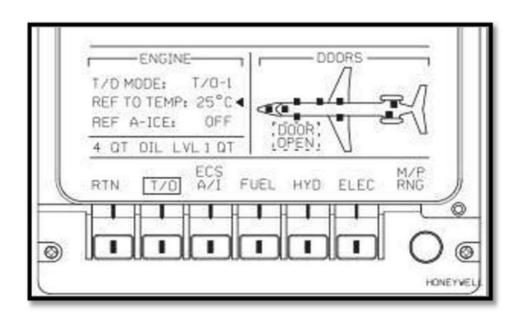

#### MULTI-FUNCTION DISPLAY - MFD

The MFD (DU 2/4) is similar to DU-3, but, through its menu, you can get access to system pages, as follows:

- Take-off Page

- ECS Page

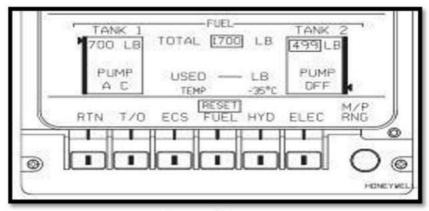

- Fuel Page

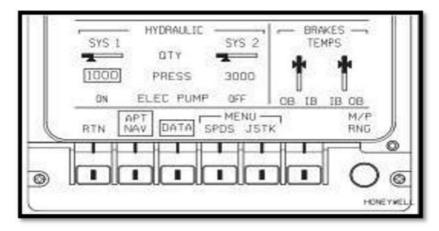

- Hydraulic/ Brake Page

- Electrical Page

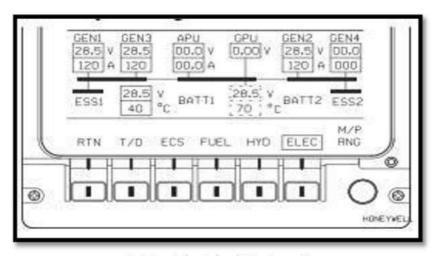

1.21 Take Off Page (MFD Partially Displayed)

1.22 Fuel System Page

1.23 Hydraulics System Page

1.24 Electrical System Page

## 5.2 NUMBERING SYSTEMS

#### INTRODUCTION

The signals in digital logic and computer systems are conveyed along individual electrical conductors and also using multiple wiring arrangements where several conductors are used to convey signals from one place to another in what is known as a bus system, the number of individual bus lines depends upon the particular bus standard employed however signals on the individual lines, no matter what they are used for nor how they are organised, can exist in only two basic states: logic 0 ('low' or 'off') or logic 1 ('high' or 'on'). Thus information within a digital system is represented in the form of a sequence of 1s and 0s known as binarydata.

Since binary numbers (particularly large ones) are not very convenient for human use, we often convert binary numbers to other forms of number that are easier to recognize and manipulate. These number systems include hexadecimal (base 16) and octal (base 8). This chapter is designed to introduce you to the different types of number system as well as the process of conversion from one type to another.

#### **DECIMAL NUMBERS**

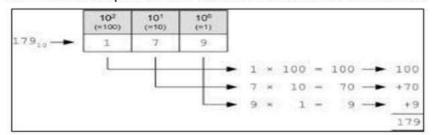

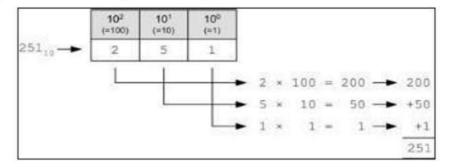

The decimal numbers (Denary) that we are all very familiar with use the base 10. In this system the weight of each digit is 10 times as great as the digit immediately to its right. The right most digit of a decimal integer (i.e. a whole number) is the unit's place (10°), the digit to its left is the ten's digit (10¹), the next is the hundred's digit (10), and so on. The valid digits in a decimal number are 0 to 9. Figures 2.1 and 2.2 show two examples of how decimal numbers are constructed

Figure 2.1: An example showing how the decimal number 179 is constructed

Figure 2.2: An example showing how the decimal number 251 is constructed

Note that we have used the suffix '10' to indicate that the number is a decimal. So, 17910 and 251

are both decimal (or base 10) numbers. The use of subscripts helps us to avoid confusion about what number base we are actually dealing with.

#### **BINARY NUMBERS**

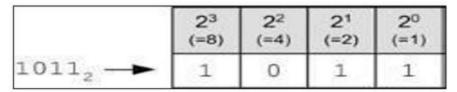

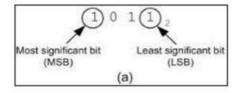

In the binary system (base 2), the weight of each digit is two times as great as the digit immediately to its right. The rightmost digit of a binary integer is the one's digit, the next digit to the left is the two's digit, next is the four's digit, then the eight's digit, and so on. The valid digits in the binary system are 0 and 1. Figure 2.3 shows an example of a binary number (note the use of the suffix '2' to indicate the number base). The binary numbers that are equivalent to the decimal numbers 0 to 9 are shown in Table 2.1. Notice how the most significant digit (MSD) is on the left and the least significant digit (LSD) appears on the right. In the table, the MSD has a weight of 2<sup>3</sup> (or 8 in decimal) whilst the LSD has a weight of 2<sup>o</sup> (or 1 in decimal). Since the MSD and LSD are represented by binary digits (either 0 or 1) we often refer to them as the most significant bit (MSB) and least significant bit (LSB) respectively, as shown in Fig.2.4.

Figure 2.3: Example of a Binary Number

Figure 2.4: MSB and LSB in Binary Numbers

#### BINARY TO DECIMAL CONVERSION

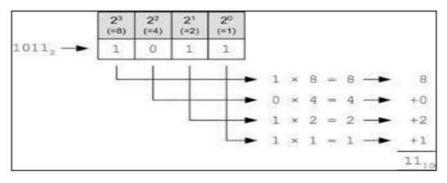

In order to convert a binary number to its equivalent decimal number we can determine the value of each successive binary digit, multiply it by the column value (in terms of the power of the base) and then simply add the values up. For example, to convert the binary number 1011, we take each digit and multiply it by the binary weight of the digit position (8, 4, 2 and 1) and add the result, as shown in Fig. 2.5below.

Figure 2.5: Example of Binary to Decimal Conversion DECIMAL TO BINARY CONVERSION

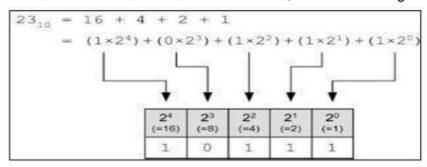

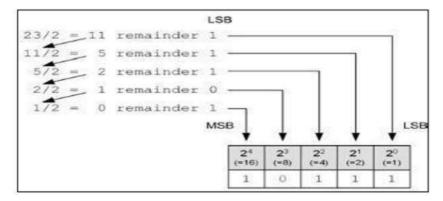

There are two basic methods for converting decimal numbers to their equivalent in binary. The first method involves breaking the number down into a succession of numbers that are each powers of 2 and then placing the relevant digit (either a 0 or a 1) in the respective digit position, as shown in Fig. 2.6. Another method involves successive division by two, retaining the remainder as a binary digit and then using the result as the next number to be divided, as shown in Figure 2.7.

Figure 2.6: Example of Decimal to Binary Conversion

#### BINARY CODED DECIMAL

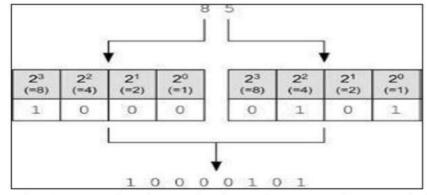

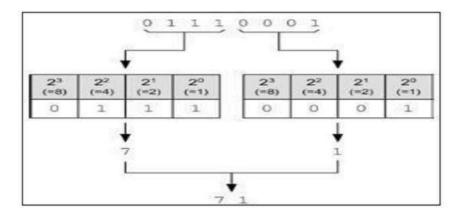

The system of binary numbers that we have looked at so far is more correctly known as natural binary. Another form of binary number commonly used in digital logic circuits is known as binary coded decimal (BCD). In this simpler system, binary conversion to and from decimal numbers involves arranging binary numbers in groups of four binary digits from right to left, each of which corresponds to a single decimal digit, as shown in Figures 2.8 and 2

Figure 2.7: Example of Decimal to Binary Conversion using Successive Division

Figure 2.8: Example of Converting the Decimal Number 85 to Binary Coded Decimal (BCD)

Figure 2.9: Example of Converting the BCD number 01110001to Decimal

#### ONE'S COMPLEMENT

The one's complement of a binary number is formed by inverting the value of each digit of the original binary number (i.e. replacing 1s with 0s and 0s with 1s) So, for example, the one's complement of the binary number 1010 is simply 0101. Similarly, the one's complement of 01110001 is 10001110. Note that if you add the one's complement of a number to the original number the result will be all 1s, as shown in Figure 2.10.

| Original binary number: |   | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

|-------------------------|---|---|---|---|---|---|---|---|---|

| One's complement:       | + | 0 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |

| Added together:         |   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

Fig: 2.10

#### TWO'S COMPLEMENT

Two's complement notation is frequently used to represent negative numbers in computer mathematics (with only one possible code for zero—unlike one's complement notation). The two's complement of a binary number is formed by inverting the digits of the original binary number and then adding 1 to the result. So, for example, the two's complement of the binary number 1001 is 0111. Similarly, the two's complement of 01110001 is 10001111. When two's complement notation is used to represent negative numbers the most significant digit (MSD) is always a 1. Figure 2.11 shows two examples of finding the two's complement of a binary number. In the case of Figure 2.11(b) it is

| Original binary number:        |   |   | 1   | 0 | 1 | 1      | - 9 | 0 | 1 | 0    | 1   |

|--------------------------------|---|---|-----|---|---|--------|-----|---|---|------|-----|

| One's complement:              |   | + | 0   | 1 | 0 | 0      |     | 1 | 0 | 1    | 0   |

| Adding 1:                      |   | + | 0   | 0 | 0 | 0      |     | 0 | 0 | 0    | 1   |

| Two's complement:              |   |   | 0   | 1 | 0 | 0      |     | 1 | 0 | 1    | 1   |

|                                |   | U | (a) | i |   |        |     |   |   |      |     |

| Original binary number:        |   | 1 | 0   | 0 | 1 | 1      | 1   | 0 | 0 | dir. |     |

|                                |   | - | -   | - | - | V 2011 | -   | - | - |      |     |

| One's complement:              | + | U | 1   | 1 | U | 0      | U   | 4 | 1 |      |     |

| One's complement:<br>Adding 1: |   |   |     |   |   | 0      |     |   | 1 |      | rry |

Figure 2.11: Method of finding the Two's Complement of a Binary Number

#### **OCTAL NUMBERS**

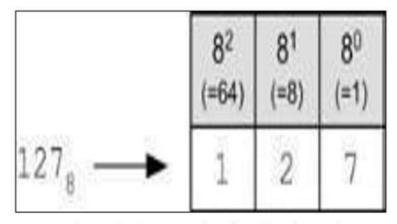

The octal number system is used as a more compact way of representing binary numbers. Because octal consists of eight digits (0 to 7), a single octal digit can replace three binary digits. Putting this another way, by arranging a binary number into groups of three binary digits (or bits) we can replace each group by a single octal digit, see Figure 2.12, the weight of each digit in an octal number is eight times as great as the digit immediately to its right. The rightmost digit of an octal number is the unit's place (8°), the digit to its left is the eight's digit (8¹), the next is the 64's digit (8²), and soon.

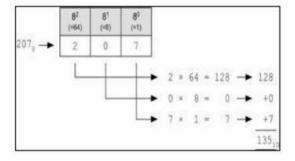

#### OCTAL TO DECIMAL CONVERSION

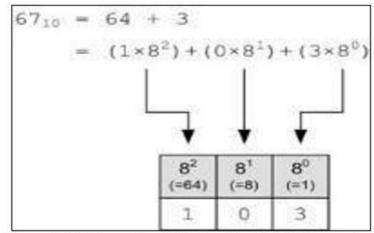

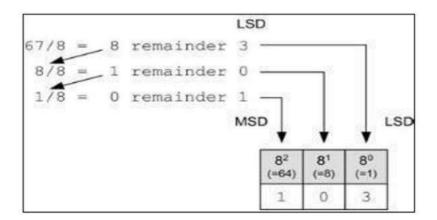

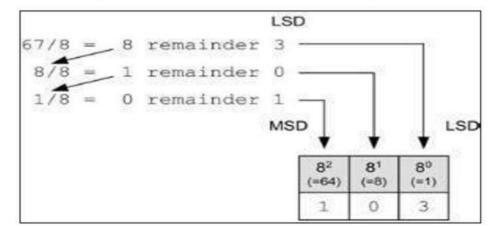

In order to convert a binary number to a decimal number we can determine the value of each successive octal digit, multiply it by the column value (in terms of the power of the base) and simply add the values up. For example, the octal number 207 is converted by taking each digit and then multiplying it by the octal weight of the digit position and adding the result, as shown in Figure 2.13.

Figure 2.12: Example of an Octal Number

Figure 2.13 Example of an Octal Number to decimal number

#### DECIMAL TO OCTAL CONVERSION

As with decimal to binary conversion, there are two methods for converting decimal numbers to octal. The first method involves breaking the number down into a succession of numbers that are each powers of 8 and then placing the relevant digit (having a value between 0 and 7) in the respective digit position, as shown in Figure 2.14.

The other method of decimal to octal conversion involves successive division by eight, retaining the remainder as a digit (with a value between 0 and 7) before using the result as the next number to be

divided, as shown in Figure 2.15. Note how the octal number is built up in reverse order i.e. with the last remainder as the MSD and the first remainder as the LSD

Figure 2.14: Example of Decimal to Octal Conversion

Figure 2.15: Example of Decimal to Octal Conversion using Successive Division

#### OCTAL TO BINARY CONVERSION

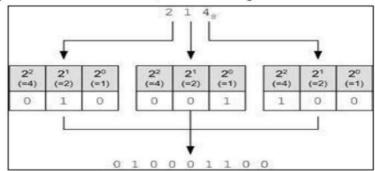

In order to convert an octal number to a binary number we simply convert each digit of the octal number to its corresponding three- bit binary value, as shown in Fig.2.16.

Figure 2.16: Example of Octal to Binary Conversion

#### BINARY TO OCTAL CONVERSION

Converting a binary number to its equivalent in octal is also extremely easy. In this case you simply need to arrange the binary number in groups of three binary digits from right to left and then convert each group to its equivalent octal number, as shown Fig. 2.17

Figure 2.17 Example of Binary to Octal Conversion HEXADECIMAL NUMBERS

Although computers are quite comfortable working with binary numbers of 8, 16, or even 32 binary digits, humans find it inconvenient to work with so many digits at a time. The hexadecimal (base 16) numbering system offers a practical compromise acceptable to both to humans and to machines. One hexadecimal digit can represent four binary digits, thus an 8-bit binary number can be expressed using two hexadecimal digits. For example, 10000011 binary is the same as 83 when expressed in hexadecimal. The correspondence between a hexadecimal (hex) digit and the four binary digits it represents is quite straightforward and easy to learn (see Table2.2).

Note that, in hexadecimal, the decimal numbers from 10 to 15 are represented by the letters A to F respectively.

#### HEXADECIMAL TO DECIMAL CONVERSION

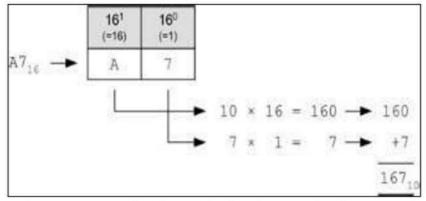

In order to convert a hexadecimal number to a decimal number we can determine the value of each successive hexadecimal digit, multiply it by the column value (in terms of the power of the base) and simply add the values up. For example, the hexadecimal number of A7 is converted by taking each digit and then multiplying it by the weight of the digit position, as shown in Figure 2.18.

| Binary | Dec.     | Hex. | Octal |  |

|--------|----------|------|-------|--|

| 0000   | 0        | 0    | 0     |  |

| 0001   | 1        | 1    | 1     |  |

| 0010   | 2        | 2    | 2     |  |

| 0011   | 3        | 3    | 3     |  |

| 0100   | 4        | 4    | 4     |  |

| 0101   | 5        | 5    | 5     |  |

| 0110   | 6        | 6    | 6     |  |

| 0111   | 7        | 7    | 7     |  |

| 1000   | 8 8      |      | 10    |  |

| 1001   | 1 9 9    |      | 11    |  |

| 1010   | 10       | A    | 12    |  |

| 1011   | 011 11 B |      | 13    |  |

| 1100   | 12       | C    | 14    |  |

| 1101   | 01 13 D  |      | 15    |  |

| 1110   | 10 14 E  |      | 16    |  |

| 1111   | 15       | F    | 17    |  |

Table 2.2: Binary, Decimal, Hexadecimal and Octal Numbers

Fig 2.18: Example of Hexadecimal To Decimal Conversion

#### DECIMAL TO HEXADECIMAL TO CONVERSION

In order to convert a decimal number to its hexadecimal equivalent you can break the number down into a succession of numbers that are each powers of 16 and then place the relevant digit (a value between 0 and F) in the respective digit position, as shown in Figure 2.19. Note how, in the case of the example shown in Figure 2.19 (b) the letters F and E respectively replace the decimal numbers 15 and 14.

Figure 2.19 (a) & (b): Example of Decimal to Hexadecimal Conversion

#### HEXADECIMAL TO BINARY CONVERSION

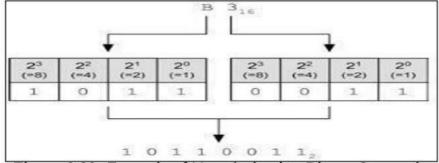

In order to convert a hexadecimal number to a binary number we simply need to convert each digit of the hexadecimal number to its corresponding four-bit binary value, as shown in Figure 2.20.

Figure 2.20: Example of Hexadecimal to Binary Conversion

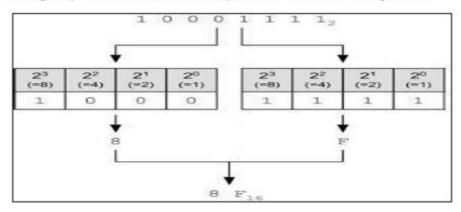

#### BINARY TO HEXADECIMAL CONVERSION

Converting a binary number to its equivalent in hexadecimal is also extremely easy. In this case you simply need to arrange the binary number in groups of four binary digits working from right to left before converting each group to its hexadecimal equivalent, as shown Figure 2.2

Figure 2.21: Example of Binary to Hexadecimal Conversion

## 5.3 DATA CONVERSION

#### INTRODUCTION

Because signals in the real world exist in both digital (on/off) and analogue (continuously variable) forms. Computer systems need to be able to accept and generate both types of signal as inputs and outputs respectively. Because of this, there is a need for devices that can convert signals in analogue form to their equivalent in digital form, and vice versa.

#### ANALOGUE AND DIGITAL SIGNALS/DATA

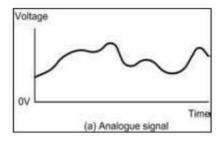

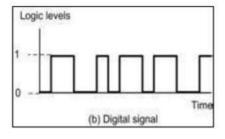

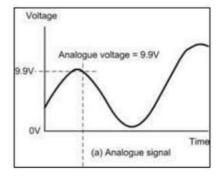

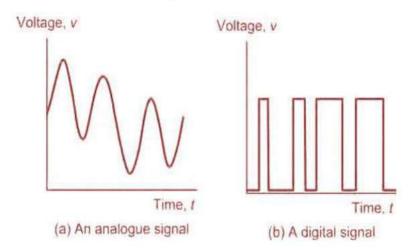

Examples of analogue and digital signals are shown in Figure 3.1. The analogue signal shown in Figure 3.1(a) consists of a continuously changing voltage level whereas the digital signal shown in Figure 3.1(b) consists of a series of discrete voltage levels that alternate between logic 0 ('low' or 'off') and logic 1 ('high' or'on').

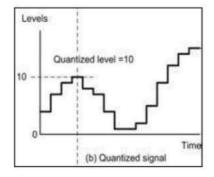

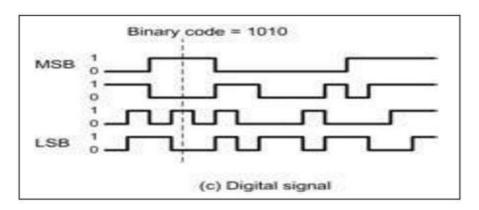

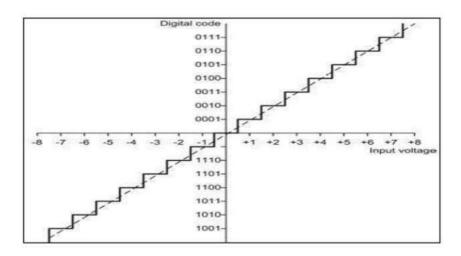

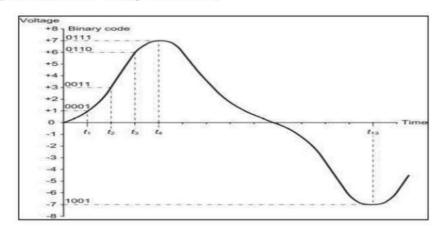

The actual voltages used to represent the logic levels are determined by the type of logic circuitry employed however logic 1 is often represented by a voltage of approximately +5V and logic 0 by a voltage of 0V. In order to represent an analogue signal using digital codes it is necessary to approximate (or quantize) the signal into a set of discrete voltage levels as shown in Figure 3.2. The sixteen quantization levels for a simple analogue to digital converter using a four-bit binary code are shown in Fig. 3.4 above. Note that, in order to accommodate analogue signals that have both positive and negative polarity we have used the two's complement representation to indicate negative voltage levels. Thus, any voltage represented by a digital code in which the MSB is logic 1 will be negative. Figure 3.5 shows how atypical analogue signal would be quantized into voltage levels by sampling at regular intervals (t1, t2, t3, etc).

Figure 3.1: Example of (a) Analogue and (b) Digital Signals

Figure 3.2: The process of quantizing an analogue signal into its digital equivalent

#### OPERATION OF DIGITAL TO ANALOGUE CONVERTER

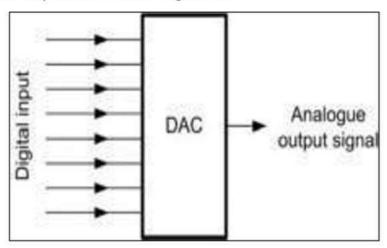

The basic digital to analogue converter (DAC) has a number of digital inputs (often 8, 10, 12, or 16) and a single analogue output, as shown in Figure 3.3.

Figure 3.3: Basic DAC Arrangement

Figure 3.4: Quantization levels for a simple analogue to digital converter using a four – binary code

(Note the use of the two's complement to indicate negative voltage levels)

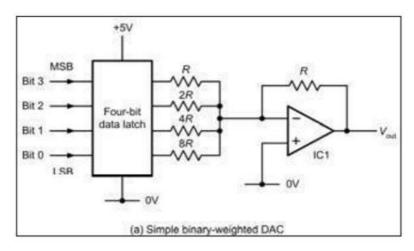

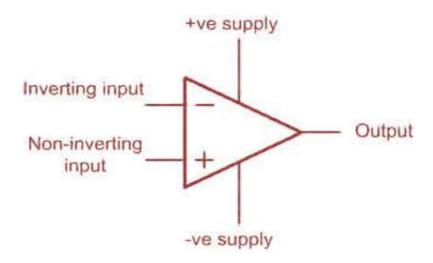

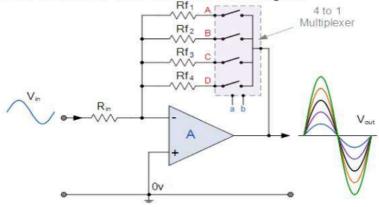

The simplest form of digital to converter shown in Fig. 3.6 below, buses a set of binary weighted resistors to define the voltage gain of an operational summing amplifier and a four-bit binary latch to store the binary input whilst it is being converted.

Figure 3.5: A bipolar analogue signal quantized into voltage levels by sampling intervals (t1, t2, t3, etc.)

| Bit     | Voltage gain   |

|---------|----------------|

| 3 (MSB) | -R/R = -1      |

| 2       | -R/2R = -0.5   |

| 1       | -R/4R = -0.25  |

| 0 (LSB) | -R/8R = -0.125 |

Table 3.1: Voltage gain for the simple DAC

| Bit 3 | Bit 2 | Bit I | Bit 0 | Output voltage |

|-------|-------|-------|-------|----------------|

| O     | 0     | 0     | O     | ov             |

| O     | O     | O     | 1     | -0.625V        |

| o     | 0     | 1     | O     | -1.250V        |

| O     | 0     | 1     | 1     | -1.875V        |

| O     | 1     | 0     | O     | -2.500V        |

| O     | 1     | O     | 1     | -3.125V        |

| O     | 1     | 1     | O     | -3.750V        |

| O     | 1     | 1     | 1     | -4.375V        |

| 1     | O     | O     | O     | -5.000V        |

| 1     | 0     | 0     | 1     | -5.625V        |

| 1     | O     | 1     | O     | -6.250V        |

| 1     | O     | 1     | 1     | -6.875V        |

| 1     | 1     | O     | O     | -7.500V        |

| 1     | 1     | 0     | 1     | -8.125V        |

| 1     | 1     | 1     | O     | -8.750V        |

| 1     | 1     | 1     | 1     | -9.375V        |

Table 3.2: Output voltages produced by the simple DAC

Figure 3.6: Simple DAV Arrangements

Note that, since the amplifier is connected in inverting mode, the analogue output voltage will be negative rather than positive. However, a further inverting amplifier stage can be added at the output in order to change the polarity if required. The voltage gain of the inputs to the operational amplifier (determined by the ratio of feedback to input resistance and taking into account the inverting configuration) is shown in Table 3.1. If we assume that the logic levels produced by the four-bit data latch are 'ideal' (such that logic 1 corresponds to +5V and logic 0 corresponds to 0V) we can determine the output voltage corresponding to the eight possible input states by summing the voltages that will result from each of the four inputs taken independently. For example, when the output of the latch takes the binary value 1010 the output voltage can be calculated from the relationship:

$$V_{out} = (-1^{5}) + (-0.5^{0}) + (-0.25^{5}) + (-0.125^{0}) = -6.25 \text{ V}$$

Similarly, when the output of the latch takes the binary value 1111 (the maximum possible) the output voltage can be determined from:

$$V_{out} = (-1^5) + (-0.5^5) + (-0.25^5) + (-0.125^5) = -9.375 V$$

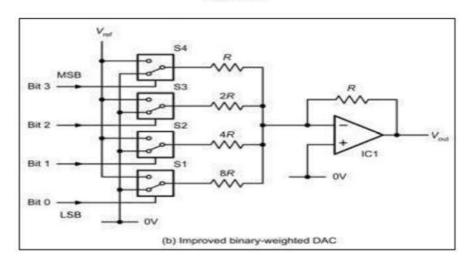

The complete set of voltages corresponding to all eight possible binary codes are given in the Table 3.2 above. An improved binary-weighted DAC This circuit operates on a similar principle but uses four analogue switches instead of a four-bit data latch. The analogue switches are controlled by the logic inputs so that the respective output is connected to the reference voltage (V<sub>ref</sub>) when the respective logic input is at logic 1 and to 0V when the corresponding logic input is at logic 0. When compared with the previous arrangement, this circuit offers the advantage that the reference voltage is considerably more accurate and stable than using the logic level to define the analogue output voltage.

A further advantage arises from the fact that the reference voltage can be made negative in which case the analogue output voltage will become positive. Typical reference voltages are -5V, -10V, +5V and +10V.

Unfortunately, by virtue of the range of resistance values required, the binary weighted DAC becomes increasingly impractical for higher resolution applications. Taking a 10-bit circuit as an example, and assuming that the basic value of R is 1 k $\Omega$ , the binary weighted values would become as shown in Table 3.3 below. In order to ensure high accuracy, all of these resistors would need to be close-tolerance types (typically  $\pm 1\%$ , or better). A more practical arrangement uses an operational amplifier in which the input voltage to the operational amplifier is determined by means of an R-2R

ladder, as shown in Figure 3.7 below. Note that only two resistance values are required and that they can be any convenient value provided that one value is double the other.

| Bit   | Resistance |

|-------|------------|

| Bit 0 | 512 kΩ     |

| Bit 1 | 256 kΩ     |

| Bit 2 | 128 kΩ     |

| Bit 3 | 64 kΩ      |

| Bit 4 | 32 kΩ      |

| Bit 5 | 16 kΩ      |

| Bit 6 | 8 kΩ       |

| Bit 7 | 4 kΩ       |

| Bit 8 | 2 kΩ       |

| Bit 9 | 1 kΩ       |

Table 3.3

Figure 3.7: Simple DAV Arrangements relatively easy to manufacture matched resistances of close tolerance and high-stability on an integrated circuit chip).

#### OPERATION OF ANALOGUE TO DIGITAL CONVERSION

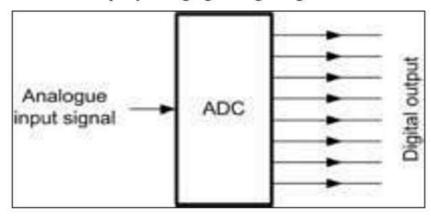

The basic analogue to digital converter (ADC) has a single analogue input and a number of digital outputs (often 8, 10, 12, or 16 lines), as shown in Figure 3.8.

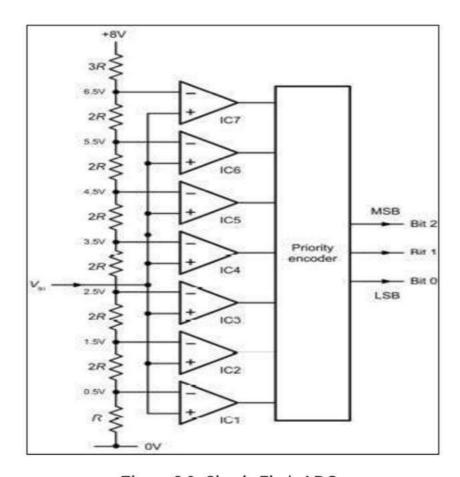

Various forms of analogue to digital converter are available for use in different applications including multi-channel ADC with up to 16 analogue inputs. The simplest form of ADC is the flash converter shown in Figure 3.9. In this type of ADC the incoming analogue voltage is compared with a series of fixed reference voltages using a number of operational amplifiers (IC1 to IC7 in Figure 3.10).

When the analogue input voltage exceeds the reference voltage present at the inverting input of a particular operational amplifier stage the output of that stage will go to logic 1. So, assuming that the

analogue input voltage is 2V, the outputs of IC1 and IC2 will go to logic 1 whilst the remaining outputs will be at logic 0. The priority encoder is a logic device that produces a binary output code that indicates the value of the most significant logic 1 received on one of its inputs. In this case, the output of IC2will be the most significant logic 1 and hence the binary output code generated will be 010 as shown in Figure 3.10 above. Flash ADC are extremely fast in operation (hence the name) but they become rather impractical as the resolution increases. For example, an 8- bit flash ADC would require 256 operational amplifier comparators and a 10-bit device would need a staggering 1,024 comparator stages. Typical conversion times for a flash ADC lie in the range 50 ns to 1 µs so this type of ADC is ideal for 'fast' or rapidly changing analogue signals.

Figure 3.8: Basic ADC Arrangement

Figure 3.9: Simple Flash ADC

| Input                         | Output |       |       |

|-------------------------------|--------|-------|-------|

| Input                         | Bit 2  | Bit 1 | Bit 0 |

| V <sub>srx</sub> < 0.5V       | 0      | 0     | 0     |

| 0.5V < V <sub>in</sub> < 1.5V | 0      | 0     | 1     |

| 1.5V < V <sub>in</sub> < 2.5V | 0      | 1     | 0     |

| 2.5V < V <sub>m</sub> < 3.5V  | 0      | 1     | 1     |

| 3.5V < V <sub>in</sub> < 4.5V | - 1    | 0     | 0     |

| 4.5V < V <sub>in</sub> < 5.5V | .1     | O     | 1     |

| 5.5V < V <sub>in</sub> < 6.5V | - 1    | 1     | 0     |

| V > 6.5V                      | - 1    | 1     | - 1   |

Figure 3.10

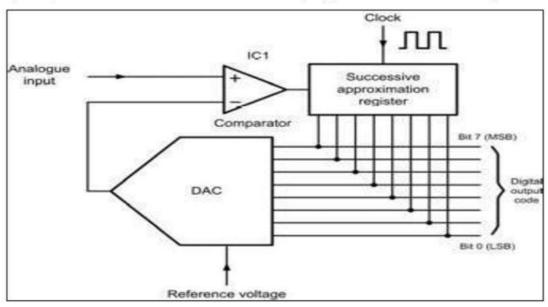

Due to their complexity, flash ADC are relatively expensive. A successive approximation ADC is shown in Figure 3.11. This shows an 8-bit converter that uses a DAC (usually based on an R- 2R ladder) together with a single operational amplifier compare at or (IC1) and a successive approximation register (SAR). The 8-bit output from the SAR is applied to the DAC and to an 8bit output latch. A separate end of conversion (EOC) signal (not shown in Fig. 3.12) is generated to indicate that the conversion process is complete and the data is ready for use.

When a start conversion (SC) signal is received, successive bits within the SAR are set and reset according to the output from the comparator. At the point at which the output from the comparator reaches zero, the analogue input voltage will be the same as the analogue output from the DAC and, at this point, the conversion is complete.

The end of conversion signal is then generated and the 8-bit code from the AR is read as a digital output code. Successive approximation ADC are significantly slower than flash types and typical conversion times (i.e. the time between the SC and EOC signals) are in the range 10  $\mu$ s to 100  $\mu$ s. Despite this, conversion times are fast enough for most non-critical applications and this type of ADC is relatively simple and available at low-cost. A ramp-type ADC is shown in Fig. 3.12.

Figure 3.11: A Successive Approximation ADC

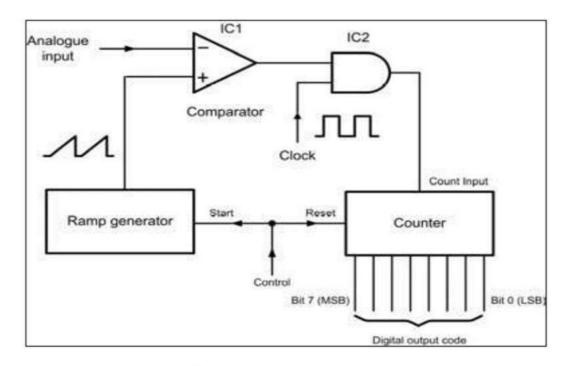

Figure 3.12 Ramp type ADC

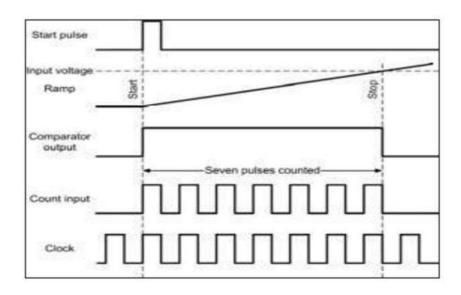

This type of ADC uses a ramp generator and a single operational amplifier comparator, IC1. The output of the comparator (either a 1 or a 0 depending on whether the input voltage is greater or less than the instantaneous value of the ramp voltage). The output of the comparator is used to control a logic gate (IC2) which passes a clock signal (a square wave of accurate frequency) to the input of a pulse counter whenever the input voltage is greater than the output from the ramp generator. The pulses are counted until the voltage from the ramp generator exceeds that of the input signal, at which point the output of the comparator goes low and no further pulses are passed into the counter. The number of clock pulses counted will depend on the input voltage and the final binary count can thus provide a digital representation of the analogue input. Typical waveforms for the ramp-type waveform are shown in Fig.3.13.

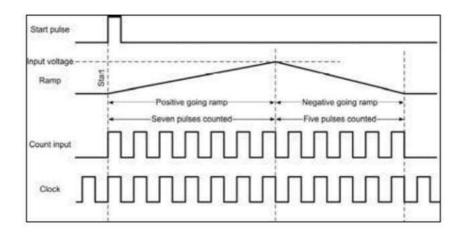

Finally, the dual-slope ADC is a refinement of the ramp-type ADC which involves a similar comparator arrangement figure 3.14 above, but uses an internal voltage reference and an accurate fixed slope negative ramp which starts when the positive going ramp reaches the analogue input voltage. The important thing to note about this type of ADC is that, whilst the slope of the positive ramp depends on the input voltage, the negative ramp falls at a fixed rate. Hence this type of ADC can provide a very high degree of accuracy and can also be made so that it rejects noise and random variations present on the input signal. The main disadvantage, however, is that the process of ramping up and down requires some considerable time and hence this type of ADC is only suitable for 'slow' signals (i.e. those that are not rapidly changing).

Typical conversion times lie in the range 500µs to 20 ms.

Figure 3.13: Waveforms for a Single-Ramp ADC

Figure 3.14: Waveforms for a Dual-Ramp ADC

### LIMITATIONS OF VARIOUS TYPE OF CONVERSION

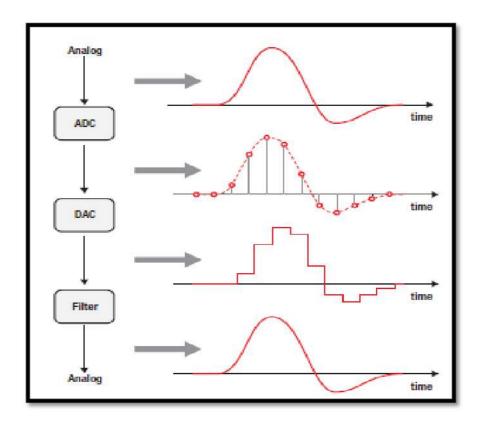

As previously discussed, analog signals are converted into digital signals so that the information is manipulated by instructions executed within a computer and then converted back to analog signals to drive analog display formats (such as hands on a clock) that are easily recognized by the crew. However, reconstructing a signal from digital-to-analog or from analog-to-digital can degrade the signal by introducing errors, also known as noise.

Reconstruction noise, as well as sampling noise from quantization, not only combine in the final signal, but also compound over multiple stages of conversion resulting in a loss of quality, or fidelity, of the original signal. All though not apparent, the waveform shown at the bottom of Figure 3-15 is a distorted version of the original waveform shown at the top. A prime example of an everyday device that converts analog signals to digital and back to analog signals is a telephone. The microphone on the phone receives sound pressure from the sender's voice, which produces an analog signal. The analog signal is converted to a digital signal which is then transmitted through the airwaves to the receiver's phone.

Figure 3.15: Conversion from analog to digital and back to analog

# 5.4 DATA BUS

### INTRODUCTION

Data bus or transmission media is defined as a twisted shielded pair transmission line consisting of the main bus and a number of stubs. There is one stub for each terminal (system) connected to the by bus. The main data bus is terminated at each end with a resistance equal to the cable's characteristic impedance. This termination makes the data bus behave electrically like an infinite transmission line. Stubs, which are added to the main bus in order to connect the terminals, provide "local" loads, and produce an impedance mismatch where added. This mismatch, if not properly controlled, produces electrical reflections and degrades the performance of the main bus.

### AIRCRAFT DATA BUS SYSTEMS:

These systems permit number of avionics equipment to communicate with one another and exchange data. These are two types:

- 1. Bidirectional (One Way)

- 2. Unidirectional (Two Way)

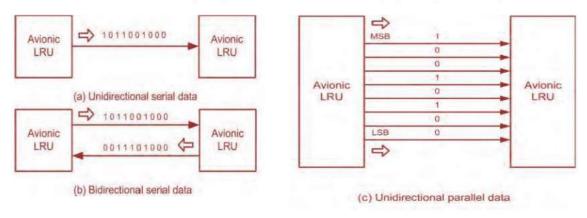

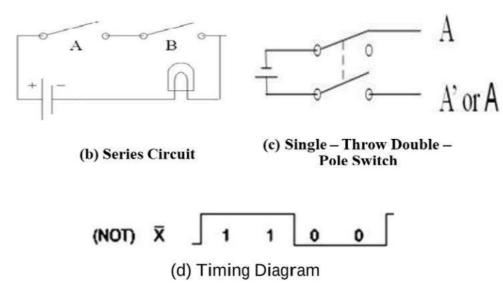

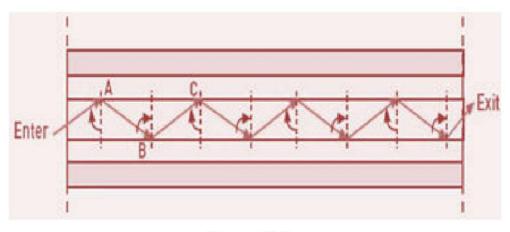

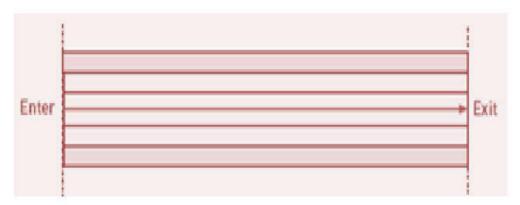

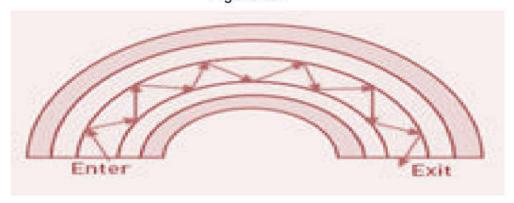

They can also be serial (one bit of data transmitted at a time) or parallel (where often 8, 16 or 32 bits of data appear as a group on a number of data lines at the same time). Because of the constraints imposed by conductor length and weight, all practical aircraft bus systems are based on serial (rather than parallel) data transfer. (Figure 4.1)

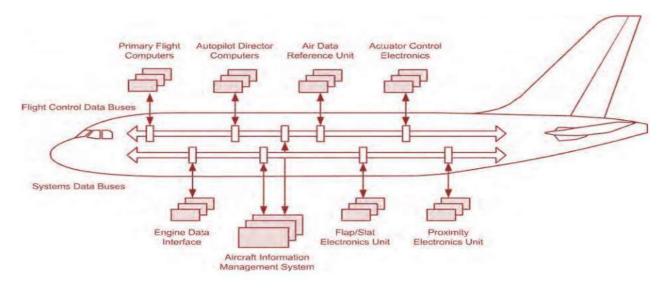

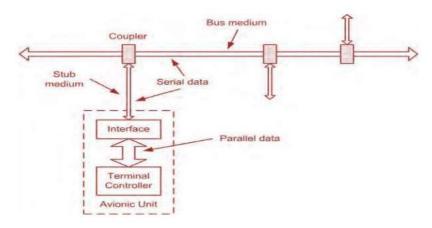

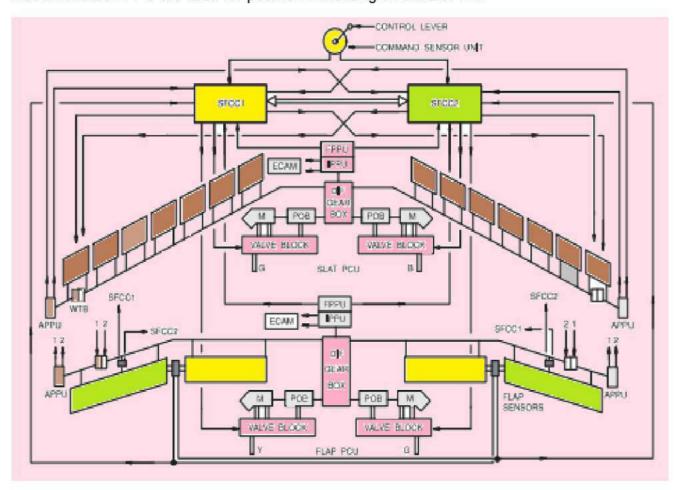

Bus systems provide an efficient means of exchanging data between the diverse avionic systems found in a modern aircraft as in Figure-4.2. Individual line replaceable units (LRU), such as the engine data interface or flap/slat electronics units shown in Fig.-4.3., are each connected to the bus by means of a dedicated bus coupler and serial interface module (not shown in Fig. 4.3).

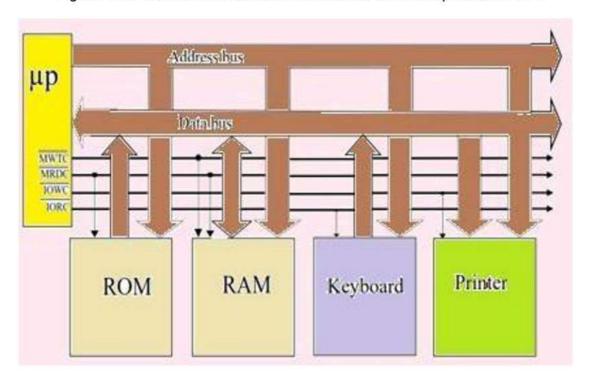

Within the LRU, the dedicated digital logic and microprocessor systems that process data locally each make use of their own local bus system. These local bus systems invariably use parallel data transfer which is ideal for moving large amounts of data very quickly but only over short distances.

Figure 4.1: Unidirectional & Bidirectional Serial & Parallel Data

Figure 4.2 : Bus Systems Implemented on a Modern Passenger Aircraft

## SERIAL BUS PRINCIPLES

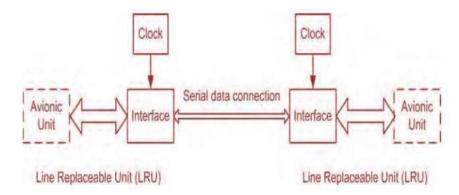

A simple system for serial data transfer between two line replaceable units, each of which comprises an avionic system in its own right, is shown in Fig. 4.3. Within the LRU data is transferred using an internal parallel data bus (Either 8, 16, 32 or 64 bits wide). The link between the two LRUs is made using a simple serial cable (often with only two, four or six conductors). The required parallel-to-serial and serial-to-parallel data conversion is carried out by a bus interface (often this is a single card or module within the LRU). The data to be transferred can be synchronous (using clock signals generated locally within each LRU) or it may be asynchronous (i.e. self-clocking). The system shown in Fig.-4.3, has the obvious limitation that data can only be exchanged between two devices.

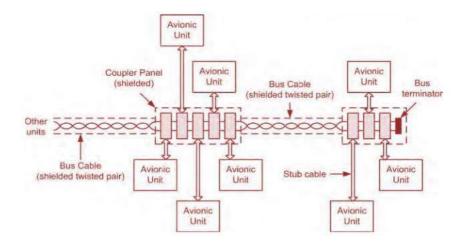

In practice we need to share the data between many LRU/avionic units. This can be achieved by the bus system illustrated in Fig.4.4. In this system, data is transferred using a shielded twisted pair (STP) bus cable with a number of coupler panels that are located at appropriate points in the aircraft (e.g. the flight deck, avionics bay, etc.).

Each coupler panel allows a number of avionic units to be connected to the bus using a stub cable. In order to optimize the speed of data transfer and minimize problems associated with reflection and mismatch, the bus cable must be terminated at each end using a matched bus terminator. Bus couplers are produced as either voltage mode or current mode units depending upon whether they use voltage or current sensing devices. Within each LRU/avionics unit, an interface is provided that performs the required serial-to-parallel or parallel-to serial data conversion, as shown in Fig.-4.5 & 4.6.

Figure 4.3: A Simple System for Serial Data Transfer Between Two AvionicSystems

Figure 4.4: A Practical Aircraft Data Bus

#### **BUS CONTROLLER**

The bus controller is responsible for directing the flow of data on the bus. While several terminals may be capable of performing as the bus controller, only one bus controller is allowed to be active at any one time. The bus controller is the only device allowed to issue commands onto the data bus. The commands may be for the transfer of data, or the control and management of the bus (referred to as mode commands).

Typically, the bus controller is a function that is contained within some other computer, such as a mission computer, a display processor, or a fire control computer. The complexity of the electronics associated with the bus controller is a function of the subsystem interface (the interface to the computer), the amount of error management and processing to be performed, and the architecture of the bus controller.

### **DESIGN FUNDAMENTALS**

## 1. EQUIPMENT INTERCONNECTION

A single transmitter is connected with up to 20 data receivers via a single twisted and shielded pair of wires. The shields of the wires are grounded at both ends and at any breaks along the length of the cable. The shields are kept as short as possible.

## 2. MODULATION

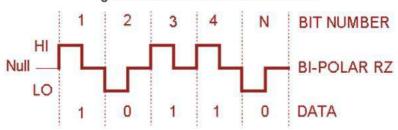

Return-To-Zero (RZ) modulation is used. The voltage levels are used for this modulation scheme.

## 3. VOLTAGE LEVELS

The differential output voltages across the transmitter output terminal with no load is described in the table - 4.1:

Figure 4.5 : A Basic Bus Interface

Figure4.6

|                  | HI (V)    | NULL (V) | LO (V)    |

|------------------|-----------|----------|-----------|

| Line A to Line B | +10 ± 1.0 | 0± 0.5   | -10 ± 1.0 |

| Line A to Ground | 5± 0.5    | 0± 0.25  | -5± 0.5   |

| Line B to Ground | -5± 0.5   | 0± 0.25  | 5± 0.5    |

Table 4.1

### ARINC SPECIFICATIONS

ARINC Specifications 419, 429, and 629 and Project Paper 453 are documents prepared by the Airlines Electronic Engineering Committee (AEEC) and published by Aeronautical Radio, Inc. These are among over 300 air transport industry avionics standards published since 1949. These documents, commonly referred to as ARINC 419, ARINC 429, ARINC 453, and ARINC 629, describe data communication systems used primarily on commercial transport airplanes. A limited

number of general aviation and military airplanes also use these data systems. The differences between the systems are described as follows.

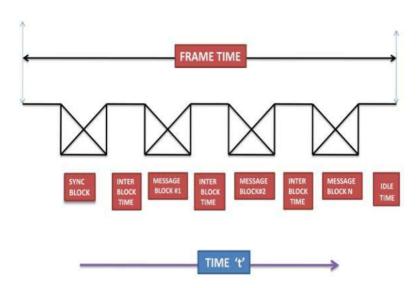

### ARINC 429

The ARINC 429 data bus has proved to be one of the most popular bus standards used in commercial aircraft. The ARINC 429 specification defines the electrical and data characteristics and protocols that are used. ARINC 429 employs a unidirectional data bus standard known as Mark 33 Digital Information Transfer System (DITS). Messages are transmitted in packets of 32-bits at a bit rate of either 12.5 or 100 kilobits per second (referred to as low and high bit rate respectively). Because the bus is unidirectional, separate ports, couplers and cables will be required when an LRU wishes to be able to both transmit and receive data. A typical data bus provides multidirectional transfer of data between multiple points over a single set of wires.

ARINC 429's simplistic one-way flow of significantly limits this capability, but the associated low cost and the integrity of the installations has provided the airlines with a system exhibiting excellent service for more than two decades. Note that a large number of bus connections may be required on an aircraft that uses sophisticated avionic systems. ARINC 429 has been installed on a wide variety of commercial transport aircraft including;

Airbus A310/A320 and 30/A340; Boeing 727, 737, 747, 757, and 767; and McDonnell Douglas MD-11. More modern aircraft (e.g. Boeing 777 & Airbus A380) use significantly enhanced bus specifications, in order to reduce the weight and size of cabling & to facilitate higher rates data than are possible with ARINC 429.

Despite these moves to faster, bidirectional bus standards, the ARINC 429 standard has proved to be highly reliable and so is likely to remain in service for many years to come. ARINC 429 is a two wire differential bus which can connect a single transmitter or source to one or more receivers. The term 'differential' simply means that neither of the two twisted wires is grounded and both convey signal voltages but of opposite polarity. This arrangement improves noise immunity which appears as a common mode signal induced on both of the conductors. Two bus speeds (High speed and low speed) are available and the data bus uses two signal wires to transmit 32 bit words. The ARINC 429 electrical characteristics are summarized in Table 4.2 below:

| 100 m                                   | + 5 $V$ , 0 $V$ , $-$ 5 $V$ (each conductor with respect to ground                                                                                                                                          |  |  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data • Bi-polar return to zero Encoding |                                                                                                                                                                                                             |  |  |

| Word Size                               | • 32 bits                                                                                                                                                                                                   |  |  |

| Bit Rate                                | <ul> <li>At High-Speed Operation bit rate of the system is 100 kilobits per second (kbps) ±1%.</li> <li>At Low-Speed Operation the bit rate of the system is Within the range 12.0 to 14.5 kbps.</li> </ul> |  |  |

Table 4.2

NOTE The selected rate is maintained within 1%.

It is important to note that the received voltage on a serial bus depends on line length and the number of receivers connected to the bus. With ARINC 429, no more than 20 receivers should be connected to a single bus. Since each bus is unidirectional, a system needs to have its own transmit bus if it is required to respond or to send messages. Hence, to achieve bidirectional data transfer it is necessary to have two separate bus connections. Since there can be only one transmitter on a twisted wire pair, ARINC 429 uses a very simple, point-to- point protocol. The transmitter is continuously sending 32-bit data words or is placed in the NULL state. Note that although there may only be one receiver on a particular bus cable the ARINC specification supports up to 20. Other, faster and more sophisticated, bus systems are found on modern aircraft.

## CLOCKING METHOD

Clocking is inherent in the data transmission. The identification of the bit interval is related to the initiation of either a HI or LO state from a previous NULL state in a bipolar RZ code. Transmission of sequential words is separated by at least four bit times of NULL (zero voltage). This eliminates the need for a separate clock signal and it makes the system self-clocking.

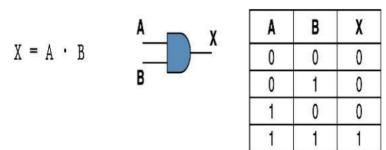

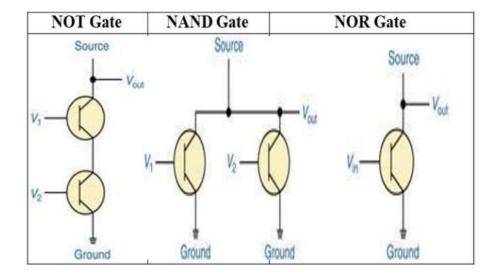

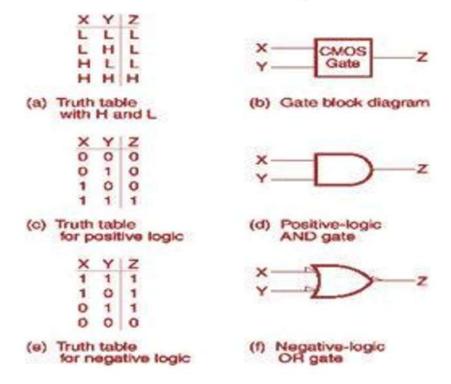

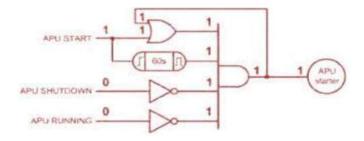

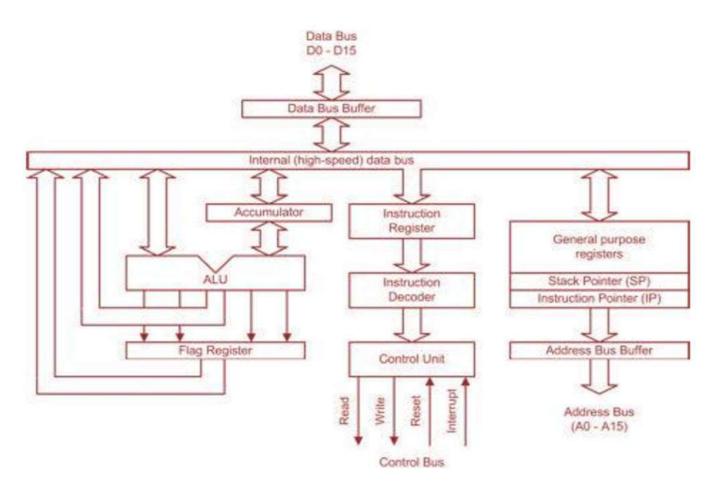

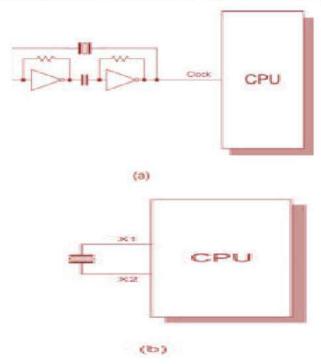

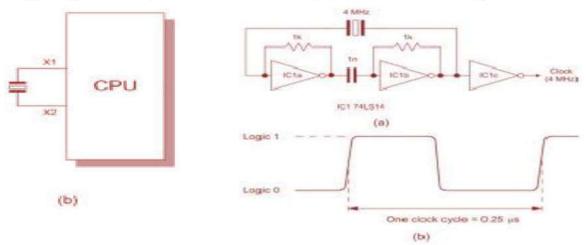

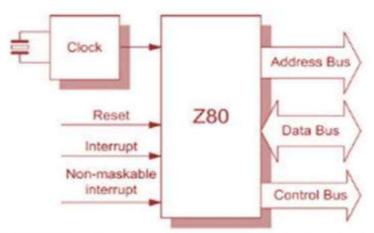

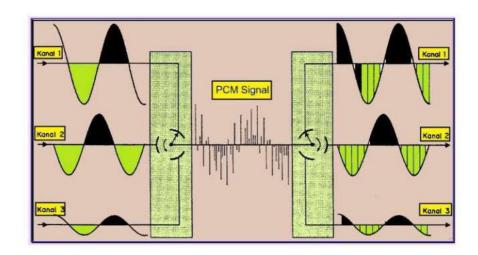

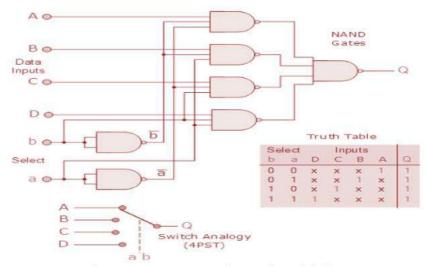

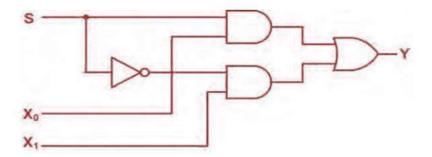

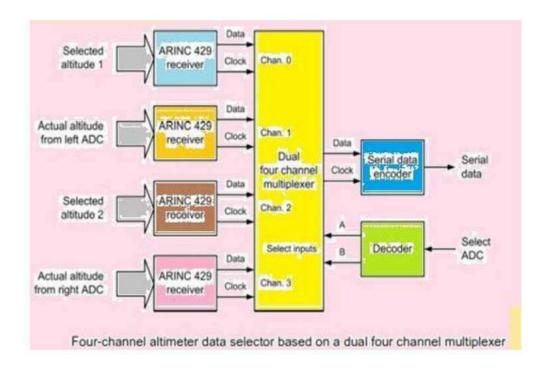

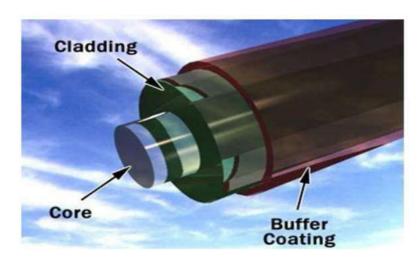

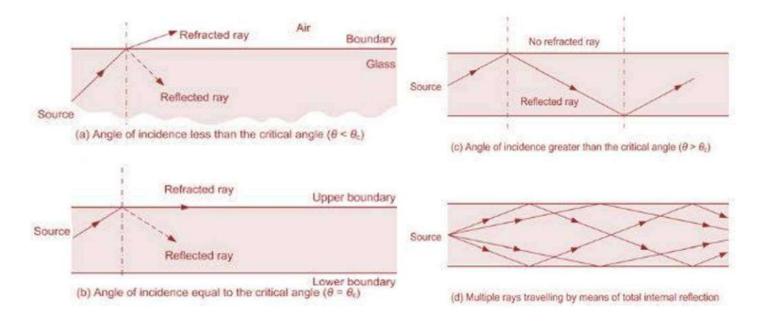

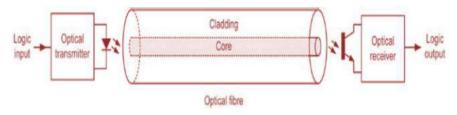

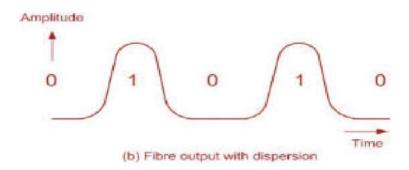

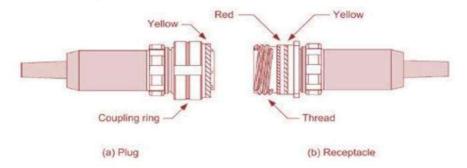

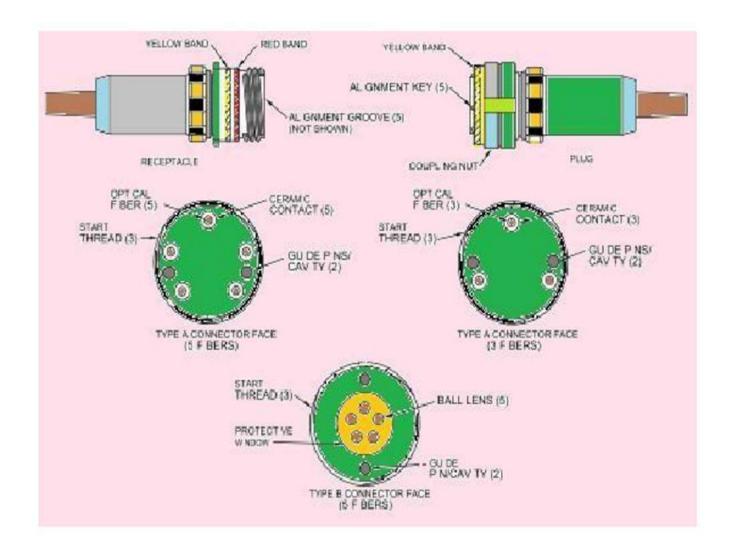

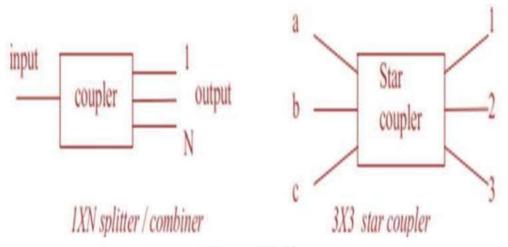

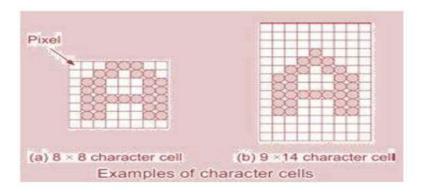

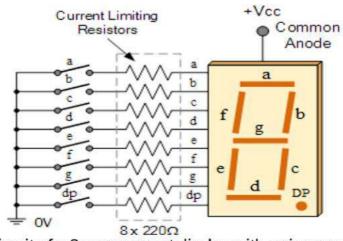

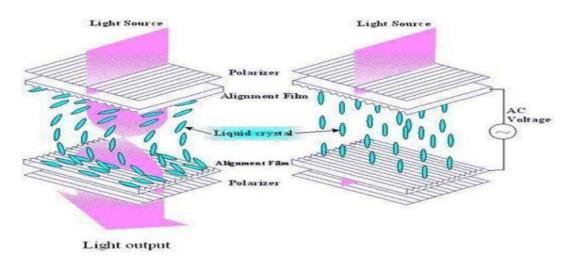

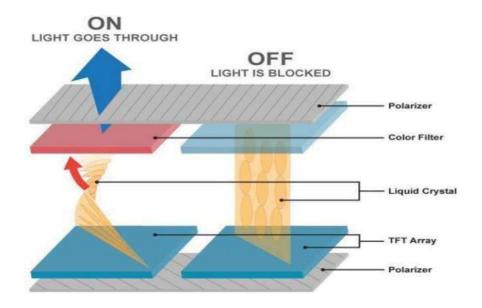

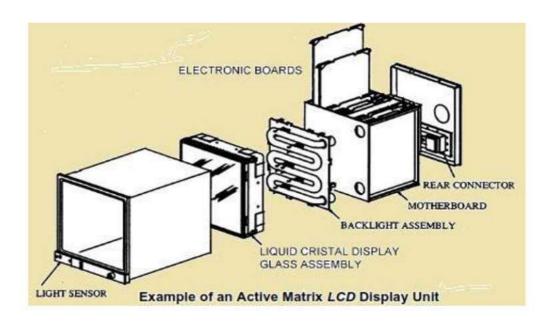

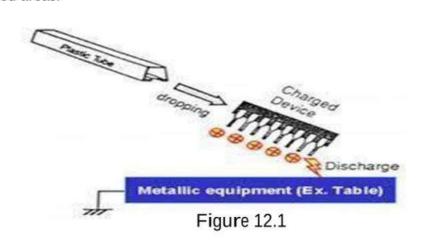

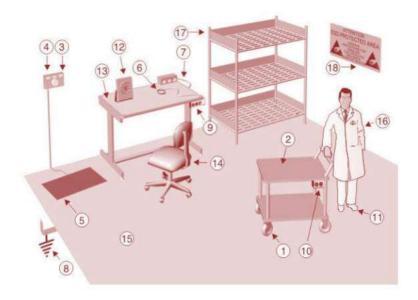

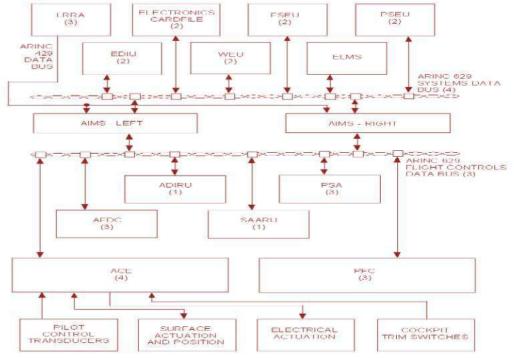

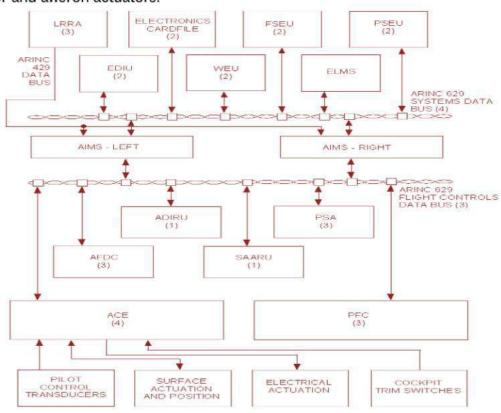

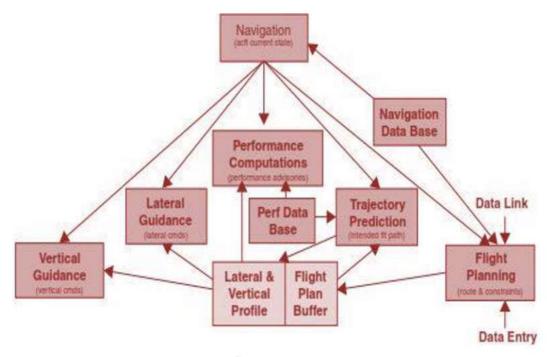

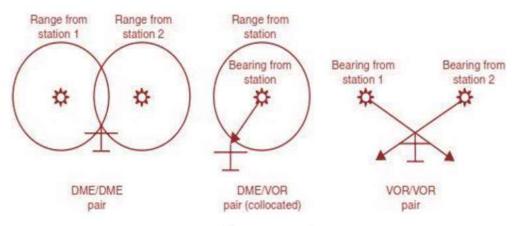

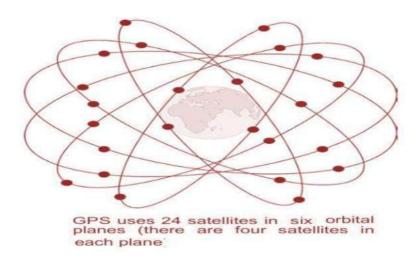

## INFORMATION RATES